# **Introduction to Fabrication**

**Reviewed 2024**

© 2020-2024 Micron Technology, Inc. All rights reserved. Information, products, and/or specifications are subject to change without notice. All information is provided on an "AS IS" basis without warranties of any kind. Statements regarding products, including statements regarding product features, availability, functionality, or compatibility, are provided for informational purposes only and do not modify the warranty, if any, applicable to any product. Drawings may not be to scale. Micron, the Micron logo, and other Micron trademarks are the property of Micron Technology, Inc. All other trademarks are the property of their respective owners.

# **Copyright guidelines**

By using any content provided by the Micron Educator Hub, you acknowledge that Micron Technology, Inc. ("Micron") is the sole owner of the content and agree that any use of the content provided by the Micron Educator Hub must comply with applicable laws and require strict compliance with these Guidelines:

- 1. Credit shall be expressly stated by you to Micron for use of the content, including any portion thereof, as follows:

- a. "© [year] Micron Technology, Inc. All Rights Reserved. Used with permission."

- 2. You may not use the content in any way or manner other than for educational purposes.

- 3. You may not modify the content without approval by Micron.

- 4. You may not use the content in a manner which disparages or is critical of Micron, its employees, or Micron's products/services.

- 5. Permission to use the content may be canceled/terminated by Micron at any time upon written notice from Micron to You if You fail to comply with the terms herein.

- 6. You acknowledge and agree that the content is provided by Micron to You on an "as is" basis without any representations or warranties whatsoever, and that Micron shall have no liability whatsoever arising from Your use of the content. Micron shall ensure that the content does not violate any statutory provisions and that no rights of third parties are infringed by the content or its publication. Otherwise, liability of the parties shall be limited to intent and gross negligence.

- 7. You acknowledge and agree that the content is the copyrighted material of Micron and that the granting of permission by Micron to You as provided for herein constitutes the granting by Micron to You of a non-exclusive license to use the content strictly as provided for herein and shall in no way restrict or affect Micron's rights in and/or to the content, including without limitation any publication or use of the content by Micron or others authorized by Micron.

- 8. Except for the above permission, Micron reserves all rights not expressly granted, including without limitation any and all patent and trade secret rights. Except as expressly provided herein, nothing herein will be deemed to grant, by implication, estoppel, or otherwise, a license under any of Micron's other existing or future intellectual property rights.

#### How to cite sources from the Micron Educator Hub

- Micron is committed to collaborate with Educators to make semiconductor memory education resources available through the Micron Educator Hub.

- The content in the Micron Educator Hub has been identified by Micron as current and relevant to our company.

- Please refer to the table on the right for proper citation.

| Use case                                                                                                | How to cite sources                                                           |

|---------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|

| a) Whole slide deck or whole document                                                                   | No additional citation required.                                              |

| Description: User uses the whole slide deck<br>or whole document AS IS, without any<br>modification     |                                                                               |

| b) Full slide or full page                                                                              | "© [year] Micron Technology, Inc. All Rights Reserved. Used with permission." |

| Description: User incorporates a full slide or<br>a full page into their own slide deck or<br>document. |                                                                               |

| c) Portion of a slide or portion of a page                                                              | This is not allowed.                                                          |

| Description: User copies a portion of a slide<br>or a portion of a page into a new slide or<br>page     |                                                                               |

# Agenda

#### **1** Introduction to Fabrication

#### 2 Basic CMOS Process Flow (Traveler)

# 1) Introduction to Fabrication

#### **Fabrication**

**Fabrication** is the process of building circuits on a silicon wafer in a **cleanroom** environment where all aspects of production (temperature, power, chemistries, moisture, contamination, etc.) are tightly controlled.

Silicon wafers are purchased from Vendors

Fabrication or Manufacturing

How long does it take to complete fabrication?

(45-140 days)

Completed wafer ready for Probe and Final Parametric testing

Picture inside a cleanroom fab

Picture inside a tool: robot that handles wafers

Picture inside a tool: dispensing photoresist in a photolithography tool

#### **Fabrication Facilities are Cleanrooms**

View of the fab from the ceiling, on the path of the AMHS (Automated Material Handling System)

#### There are hundreds of tools in a semiconductor fab

View of a tool in a fab

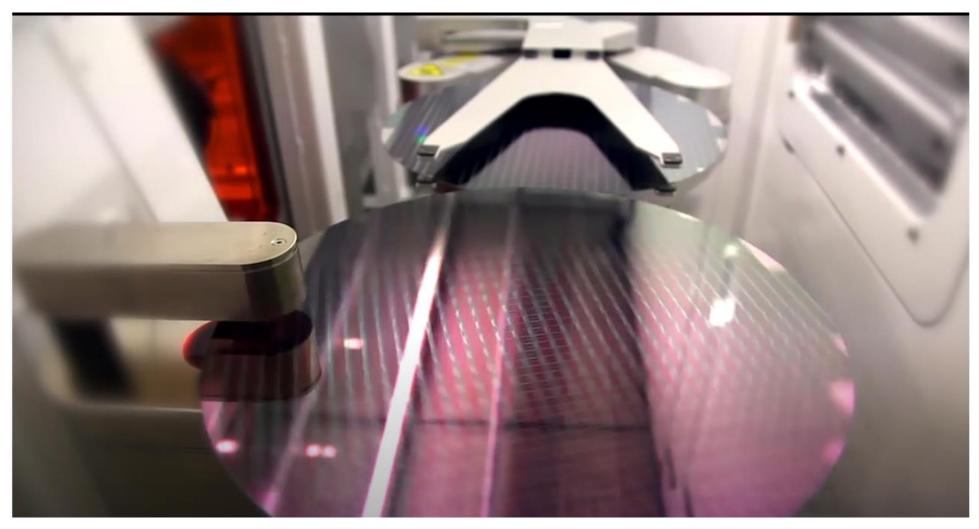

#### Automation inside a tool

Picture inside a tool: robot that handles wafers

#### **Cleanrooms & Classification Standards**

#### **Q: What Is a Cleanroom?**

**A:** A cleanroom is a room that has HEPA filtration to remove particles from the air. Cleanrooms are used for manufacturing where high levels of cleanliness and sterility are required. Common applications are medical devices, pharmaceutical and **semiconductor manufacturing**.

Note: US Fed standard in particles per ft<sup>3</sup> superseded in 2021 by ISO standard using particles per m<sup>3</sup>.

#### **ISO 14644-1 Cleanroom Standards**

| ISO Maximum Particles per m <sup>3</sup> |                  |                  |                  |                  | FED         |                |           |

|------------------------------------------|------------------|------------------|------------------|------------------|-------------|----------------|-----------|

| Class                                    | <u>&gt;</u> 0.1μ | <u>&gt;</u> 0.2µ | <u>&gt;</u> 0.3µ | <u>&gt;</u> 0.5µ | <u>≥</u> 1µ | <u>&gt;</u> 5μ | Standard  |

| ISO 4                                    | 10,000           | 2,370            | 1,020            | 352              | 83          |                | Class 10  |

| ISO 5                                    | 100,000          | 23,700           | 10,200           | 3,520            | 832         | 29             | Class 100 |

Question: Why do we wear smocks in the fab?

To protect wafers from human and other contamination

## **Semiconductor Memory Manufacturing Flow**

Start Material: Silicon is purified and formed into wafers (outside Micron).

This document focuses on this part

<u>Wafer-Level Fabrication</u>: Electronic devices (transistors, resistors, capacitors, etc.) are fabricated on the silicon wafers, and are then interconnected together into complete circuits.

<u>Probe</u>: Each die is tested for functionality, failing die are flagged. Failure data (bins) is collected for yield improvement.

<u>Param</u>: Wafer-level electrical data is collected to characterize and improve the process.

**Packaging**: Die that pass Probe are separated from the wafer and assembled into packages.

**Final Test and Burn-In**: Packaged parts are tested for functionality. Some parts are given additional tests under harsh conditions to verify reliability.

Module Assembly and Testing: Some DRAM Packaged parts are placed into Modules and further tested for functionality and reliability.

**System/SSD Testing**: NAND packaged parts may be placed into SSDs or Composite drives and further tested for performance.

**Customer!**

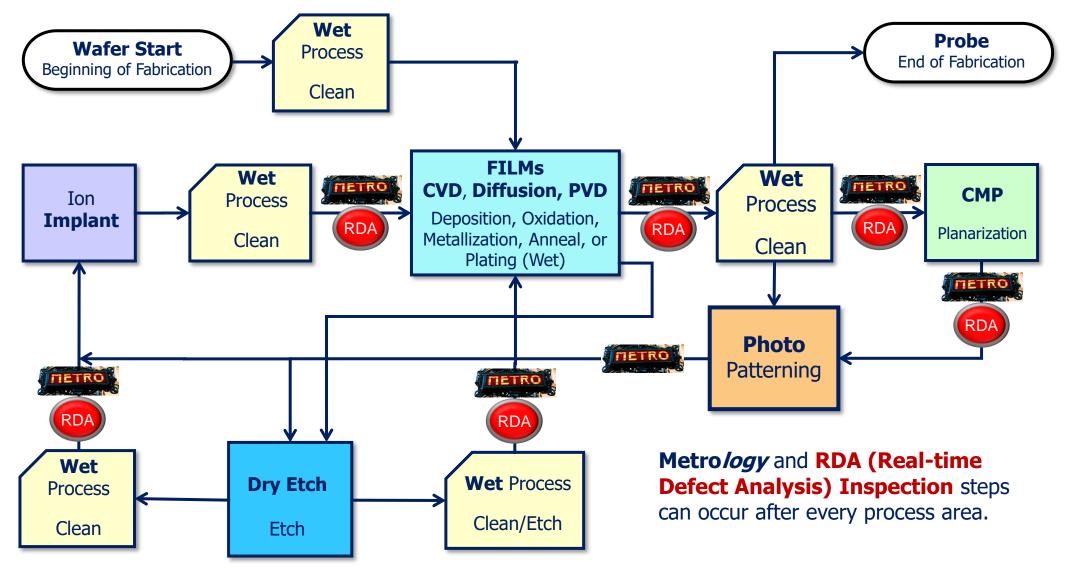

#### Wafer Processing Areas – Five Basic Actions

- 1. Creating Patterns Photolithography

- 2. Changing electrical properties Implant

3. Removing/Etching Material Dry Etch

Wet Process CMP (chemical mechanical planarization)

#### 4. Adding Material Diffusion CVD (chemical vapor deposition) PVD (physical vapor deposition) Wet Process (electroplating)

#### 5. Measuring/Inspecting

Metrology RDA (real-time defect analysis)

#### **Simplified Wafer Processing Flow**

#### **Simplified Wafer Processing Flow**

#### **Wafer Process Traveler**

A **Traveler** is the list, in order, of every step needed to make a memory chip. Years ago it was printed on cleanroom paper and "traveled" along with the box of wafers. Nowadays tracking is all performed online.

A Traveler may have more than a thousand steps!

Each Traveler step belongs to one of the 10 Fab areas.

Each Traveler step has a **Recipe** associated with it. The Recipe contains detailed instructions to process the wafer (for example: temperature, pressure, chemicals or gases used, dilution of chemicals, amount of time, etc.)

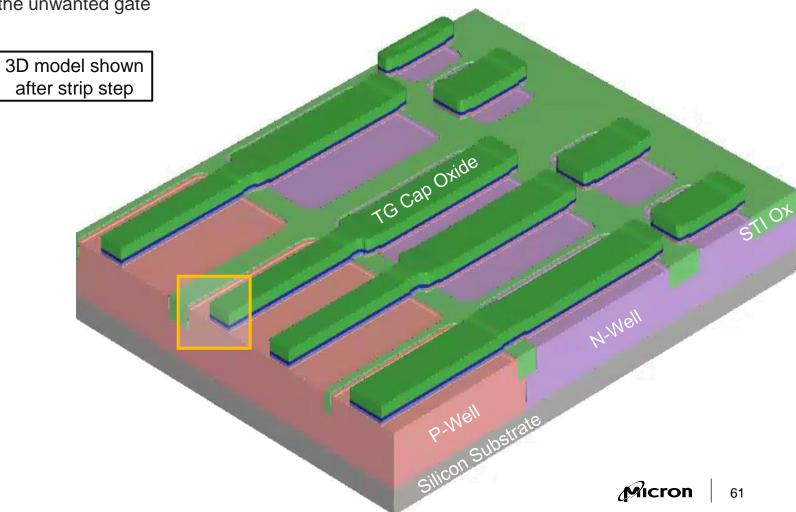

| Step # | Traveler Step                       | Area        |

|--------|-------------------------------------|-------------|

| 161    | TG - GATE HARDMASK DEPOSITION       | CVD         |

| 162    | TG - GATE PHOTO PATTERN             | РНОТО       |

| 163    | TG - GATE PHOTO ALIGNMENT           | METROLOGY   |

| 164    | TG - GATE CRITICAL DIMENSION        | METROLOGY   |

| 165    | TG - GATE DRY ETCH                  | DRY ETCH    |

| 166    | TG - GATE DRY STRIP                 | WET PROCESS |

| 167    | TG - GATE WET CLEAN                 | WET PROCESS |

| 168    | TG - GATE CRITICAL DIMENSION        | METROLOGY   |

| 169    | TG - GATE STRESS                    | METROLOGY   |

| 170    | TG - GATE PROFILE                   | METROLOGY   |

| 171    | TG - GATE INSPECTION                | RDA         |

| 172    | TG - GATE SPACER WET CLEAN          | WET PROCESS |

| 173    | TG - GATE SPACER OXIDE DEPOSITION   | CVD         |

| 174    | TG - GATE SPACER OXIDE DRY ETCH     | DRY ETCH    |

| 175    | TG - GATE SPACER OXIDE WET CLEAN    | WET PROCESS |

| 176    | TG - GATE SPACER CRITICAL DIMENSION | METROLOGY   |

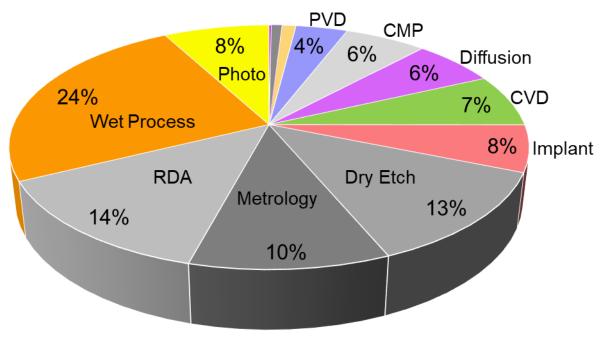

#### **Breakout of Steps by Functional Area**

- There are 10 primary "functional areas" of the fab:

- CMP: Chemical Mechanical Planarization

- CVD: Chemical Vapor Deposition

- Diffusion

- Dry Etch

- Implant

- Metrology

- Photo

- PVD: Physical Vapor Deposition

- RDA: Real time Defect Analysis

- Wet Process

- The pie chart on the right shows a typical distribution of the number of traveler steps by each functional area.

Why do you think Wet Process is the area with the highest percentage of steps? Hint: look at the slide titled Simplified Wafer Processing Flow

Micron

16

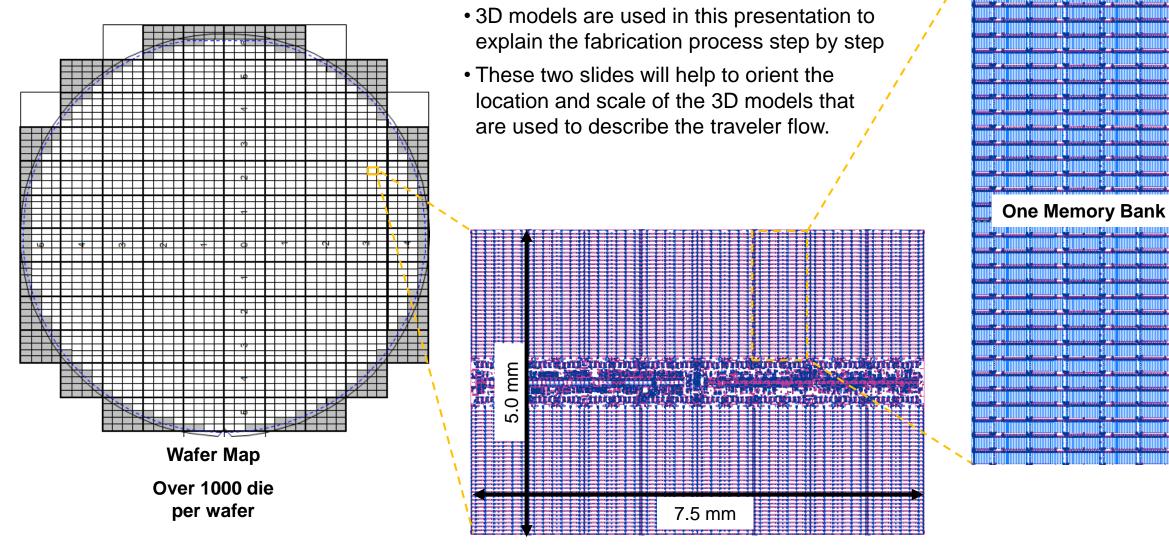

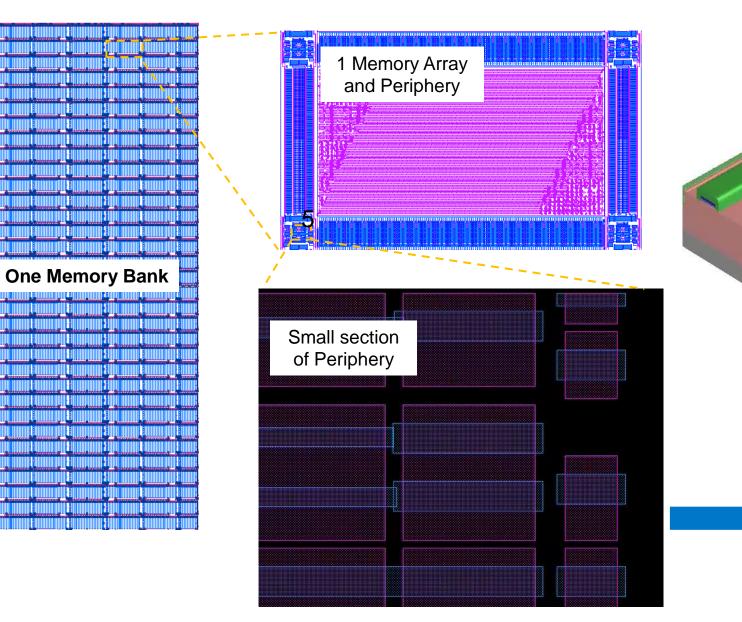

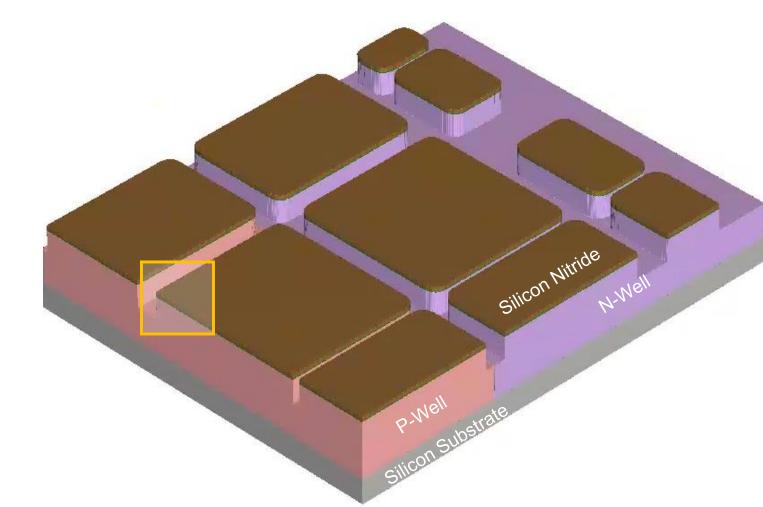

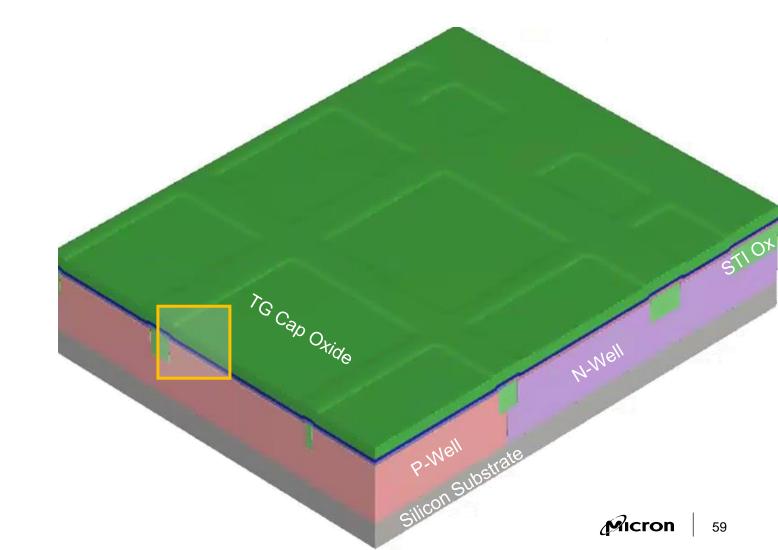

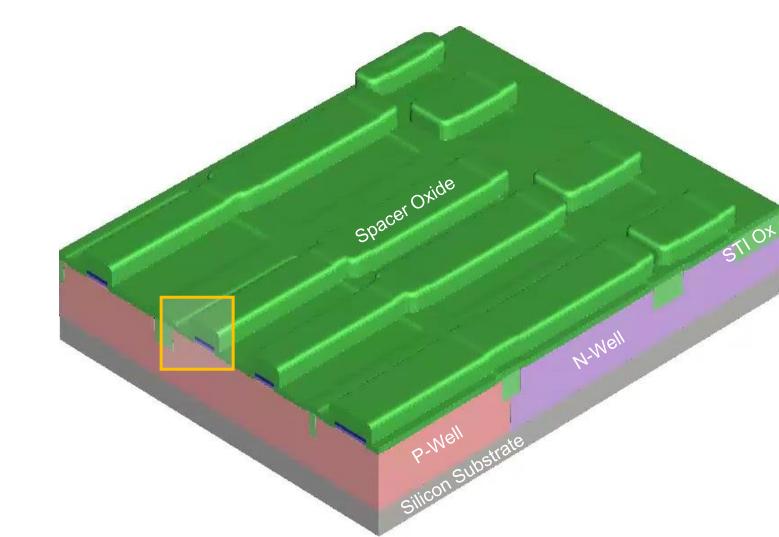

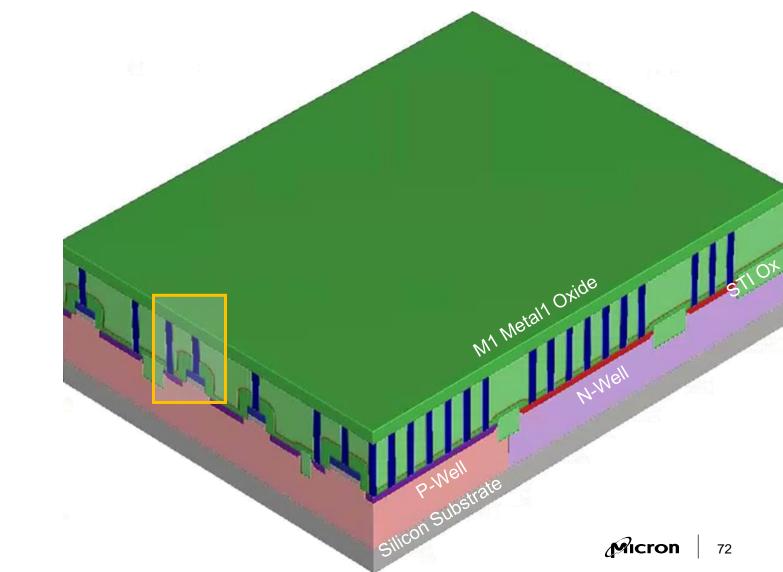

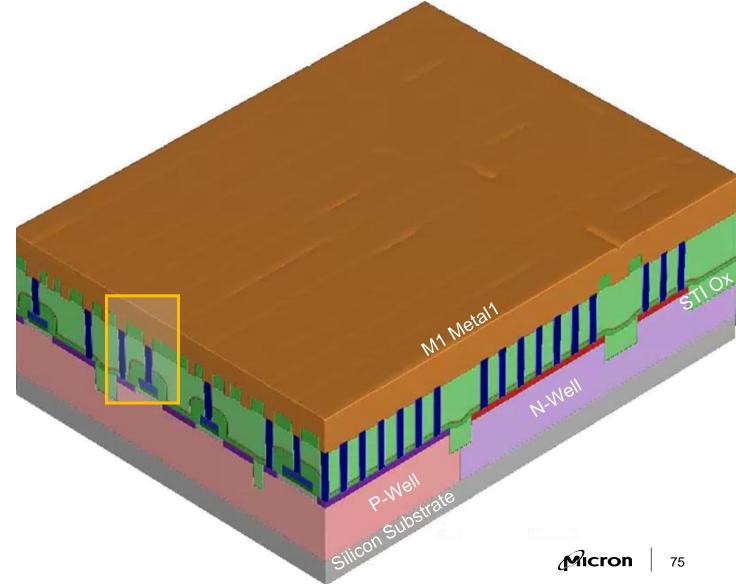

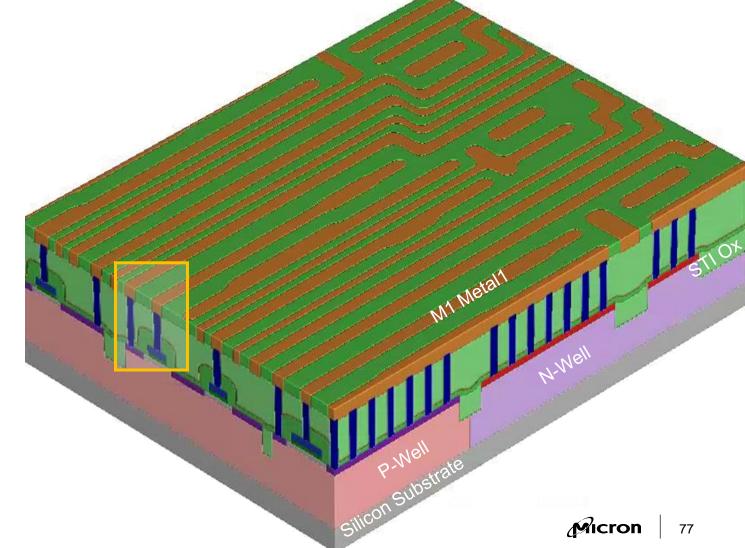

#### Zoom In to 3D Model

**One DRAM Die**

#### Zoom In to 3D Model (continued)

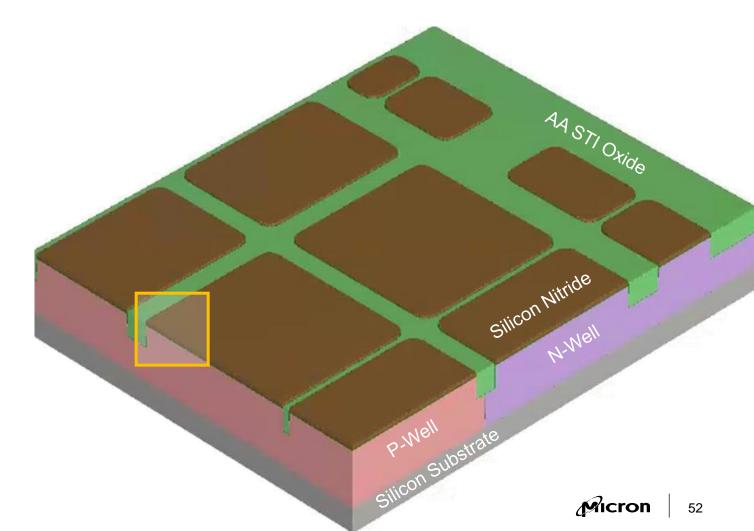

3D Model of a Small Section of CMOS Periphery

#### **Photo Mask Levels**

- During the fabrication process, patterns are created on the wafer using a series of photomasks.

- Each mask has a unique pattern

- A typical DRAM or NAND flow may have dozens of different masks

- Micron convention is to assign a 2-digit alphanumeric code to each mask.

- The table below lists the masks that we will use for our simplified CMOS flow.

| Code | Description                       |

|------|-----------------------------------|

| NW   | N-Well (for PMOS devices)         |

| PW   | P-Well (for NMOS devices)         |

| AA   | Active Areas                      |

| TG   | Transistor Gates                  |

| NA   | N-Source/Drain (for NMOS devices) |

| PA   | P-Source/Drain (for PMOS devices) |

| CN   | Contacts (Transistors to Metal1)  |

| M1   | Metal1 Interconnects              |

| BP   | Passivation and Bond Pads         |

# Basic CMOS Process Flow (Traveler)

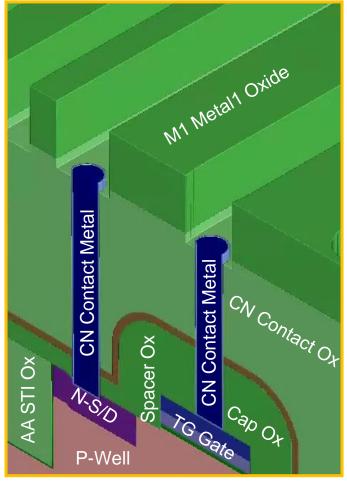

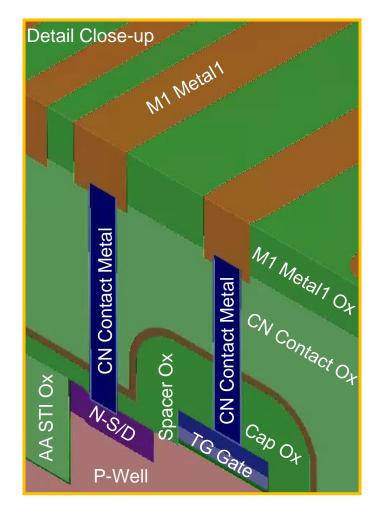

**CN Contact Metal**

N-SID

P-Well

AA STI OX

M1 Metal1 OX

CN Contact OX

Cap Ox

Contact Metal

õ

Dacer TG Gate

Micron Confidential

#### **Basic CMOS Traveler**

- In the next slides we will show a simplified traveler used to build CMOS transistors (NMOS and PMOS transistors) along with contacts and a metal routing layer.

- As new traveler steps are introduced, we will provide a brief description of the Fab Areas that perform those steps

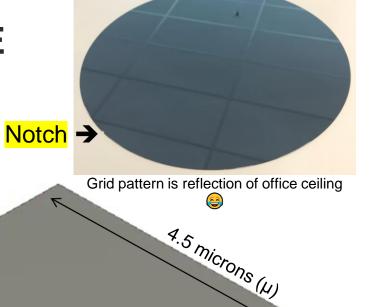

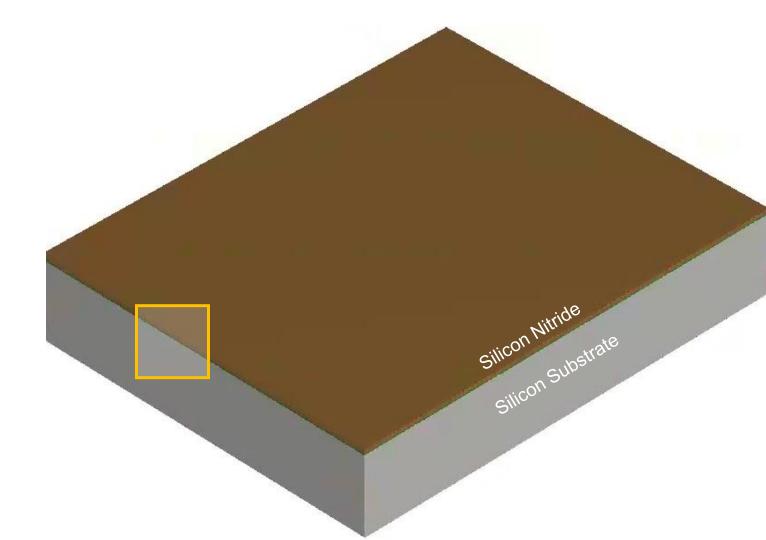

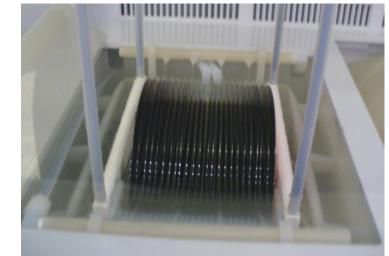

#### WAFER START with BARE SILICON SUBSTRATE

- Double-side polished bare silicon wafers (with alignment "notch"), also called Silicon Substrates, are received from our external suppliers in 25-wafer Front-Opening Shipping Boxes (FOSB)

- Wafers are transferred into a Front-Opening Unified Pod (FOUP) in which they will reside as they move from tool to tool during their whole processing "life" within the fab cleanroom

- Typical Wafer Specs:

- Thickness = less than 1 mm (3D model only shows top 1µm of Si thickness)

- Diameter = 300 mm

- Resistivity = lightly doped P-type

FOUP

3D Model views are typically only a few microns on a side

#### ...for the record... 300mm is the size of a record

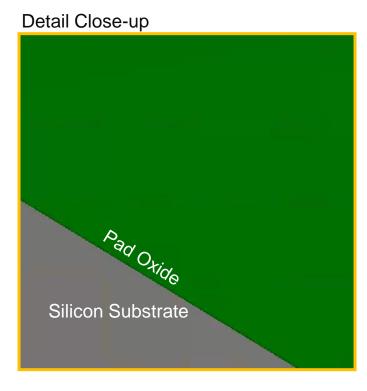

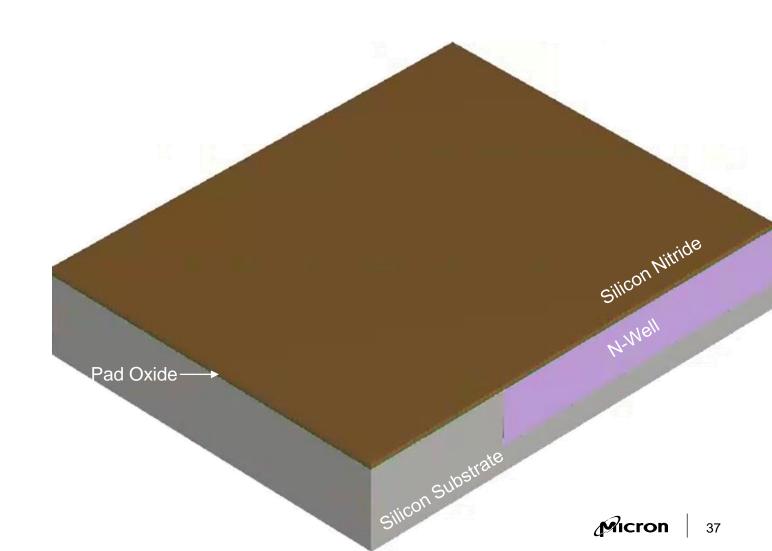

#### PAD OXIDE GROWTH [DIFFUSION]

- In the <u>Diffusion Area</u> a thin film of silicon dioxide is grown on the surface of the wafer to protect the silicon substrate from surface damage during implants and to keep the surface clean and free from defects.

- Silicon dioxide is usually referred as "oxide" and is an insulator or dielectric

- This specific oxide in this location of the traveler is sometimes called "Pad Oxide"

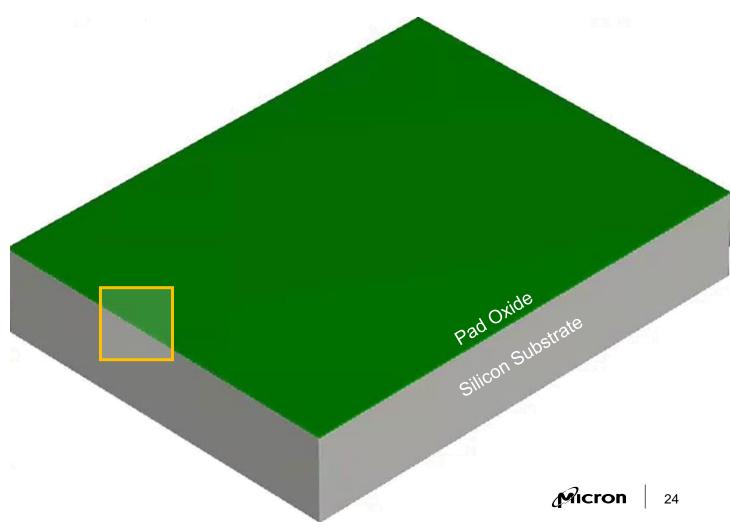

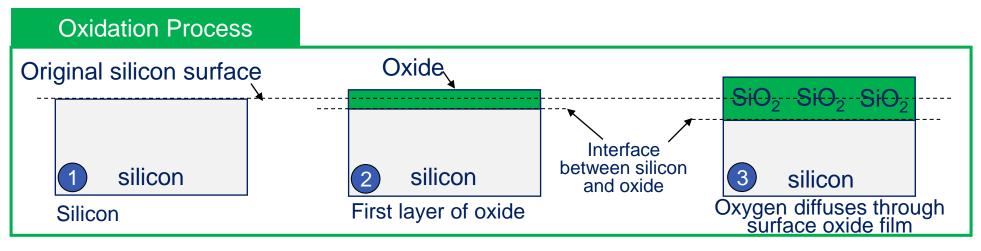

## **Oxidation (Diffusion)**

- The Diffusion area of the fab consists primarily of vertical furnace tubes where many wafers can be processed at a time (a batch process – upwards of 125-wafers at a time)

- Many different processes take place in the furnace tubes, including:

- **Oxidation** growth of a high-quality silicon dioxide layer on exposed silicon (process shown below)

- Deposition of films (similar to CVD)

- Heat treatment needed to repair damage or achieve certain electrical results

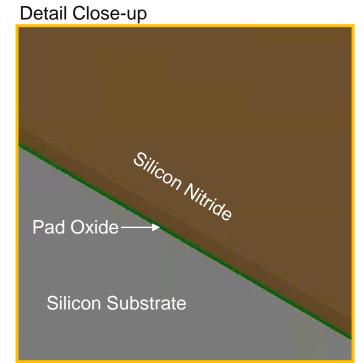

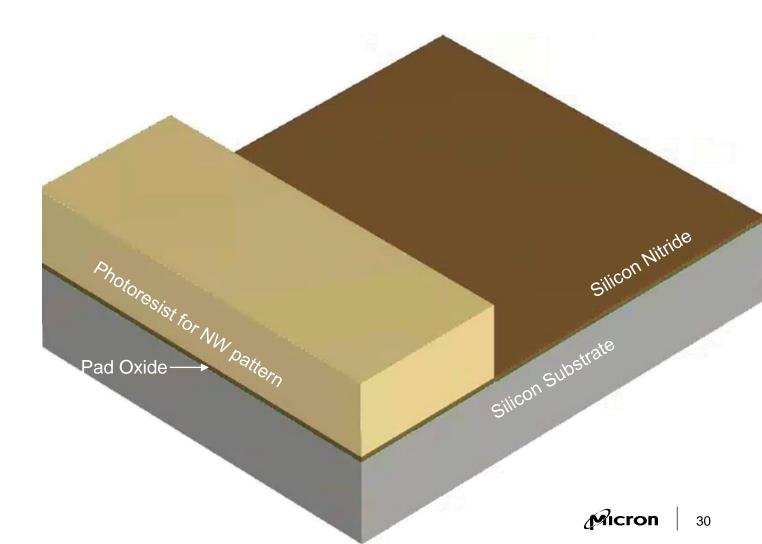

#### NITRIDE DEPOSIT [DIFFUSION]

- In the <u>Diffusion Area</u> a thin film of silicon nitride is deposited on top of the Pad Oxide. This film will be used later in the flow as a stop layer for a polishing process.

- Silicon nitride is usually referred as "nitride"

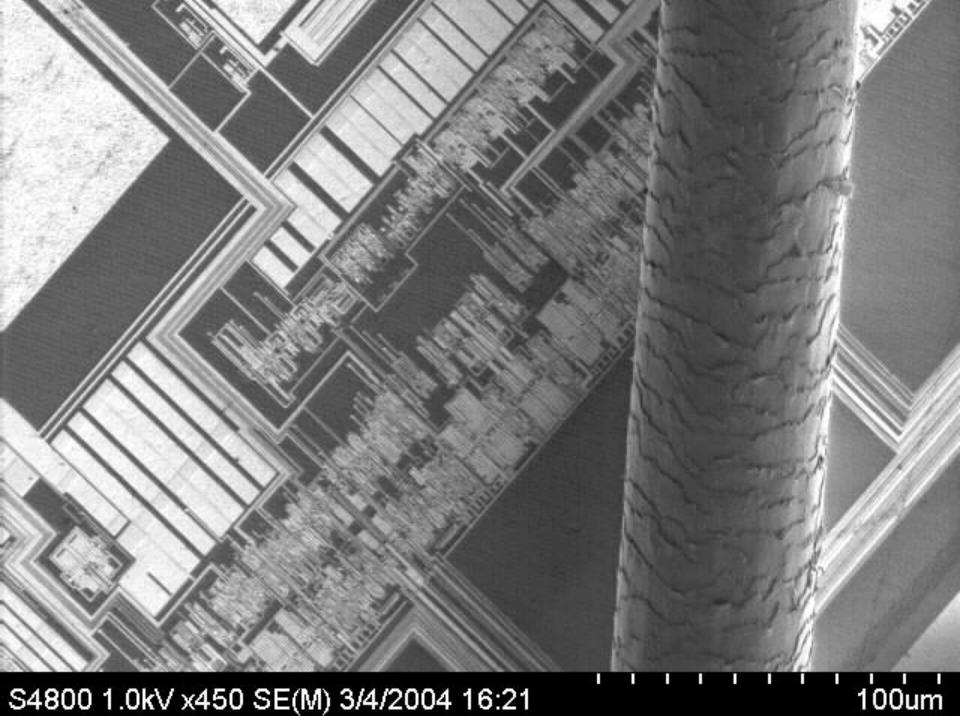

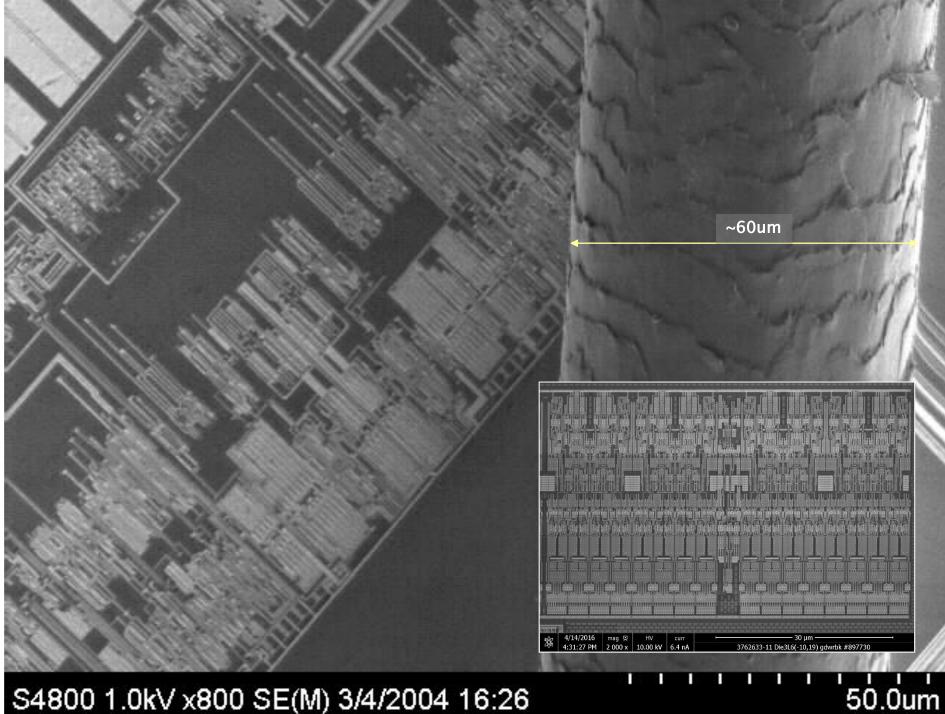

Circuit Elements with Human Hair

This hair is ~60  $\mu$  wide. Hair may range 40-120  $\mu$  wide.

Aricron 27

Circuit Elements with Human Hair

**Circuit Elements with** Human Hair

S4800 1.0kV x800 SE(M) 3/4/2004 16:26

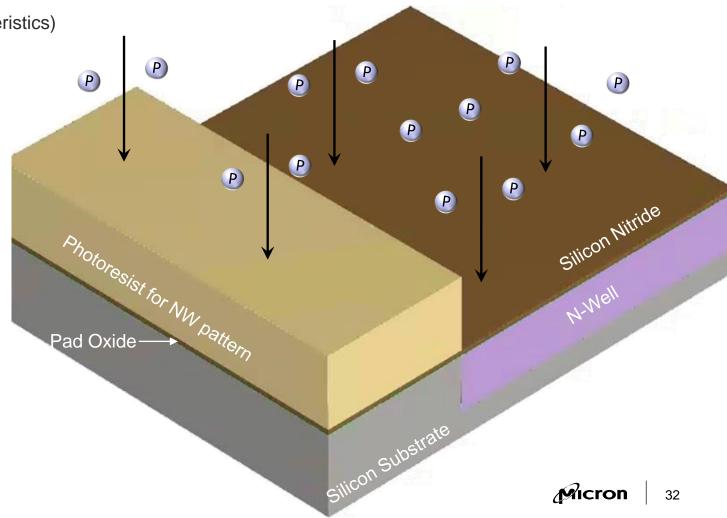

#### NW N-WELL PHOTO PATTERN [PHOTO]

- In the <u>Photolithography Area</u> the "NW" reticle or mask is used to define a pattern in photoresist. The pattern will open certain areas where N-Wells are needed for the formation of PMOS transistor devices.

- <u>Metrology:</u>

- Resist Thickness: ~ very thick to block implant

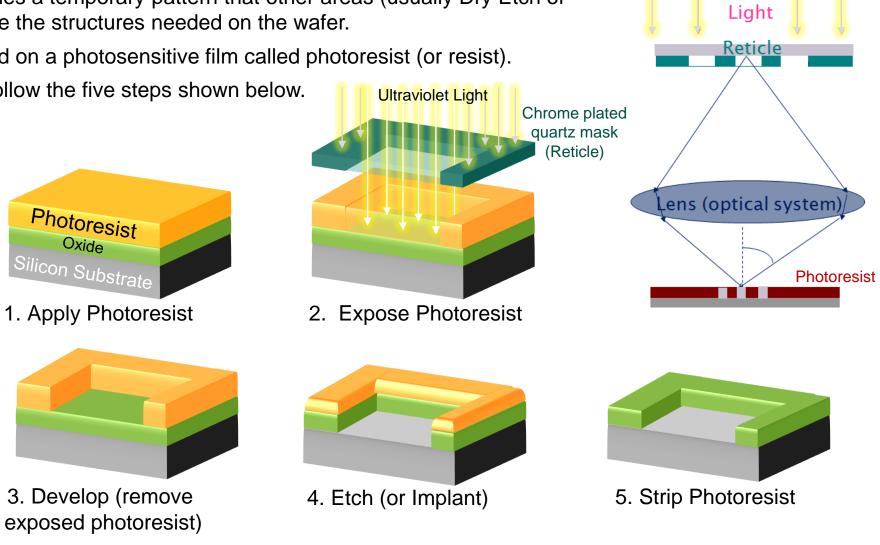

#### **Photolithography**

- The Photolithography area defines a temporary pattern that other areas (usually Dry Etch or ٠ Implant) use as a mask to create the structures needed on the wafer.

- The temporary pattern is created on a photosensitive film called photoresist (or resist). ٠

- Patterns created on the wafer follow the five steps shown below. ٠

- The first three of these steps are performed in the photolithography area

- Immersion 193nm can print ٠ features down to 37nm and EUV can achieve ~15nm

- Modern Travelers have ٠ several dozen patterning levels

- Photoresist is "sacrificial" • since it is only used temporarily to define patterns and once used any remaining film is removed.

Micron

31

#### NW N-WELL IMPLANT [IMPLANT]

- In the <u>Implant Area</u> an ion implanter shoots phosphorous ions deep into the silicon to create an N-Well. The N-Well will provide the background doping needed to form PMOS transistors. The thick photoresist prevents the ions from entering the wafer in areas where N-Wells are not needed.

- <u>Metrology:</u>

- Implant Depth: deep implant

- Implant Dose: Low (needed for transistor characteristics)

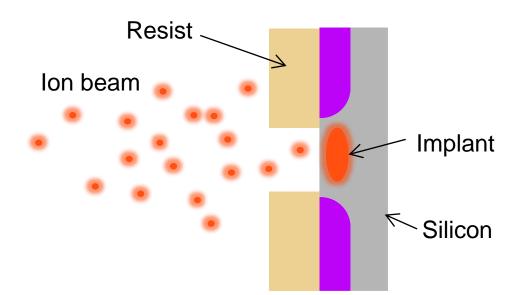

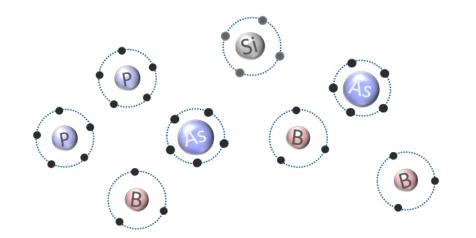

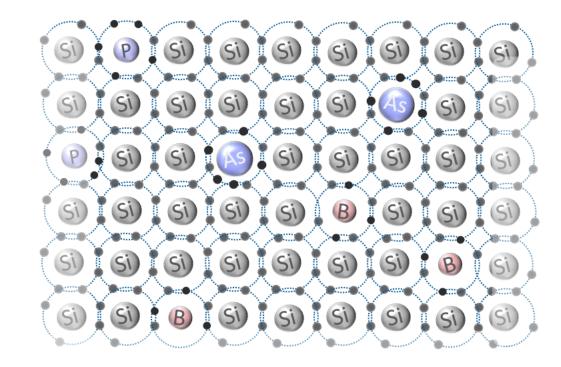

#### Ion Implantation

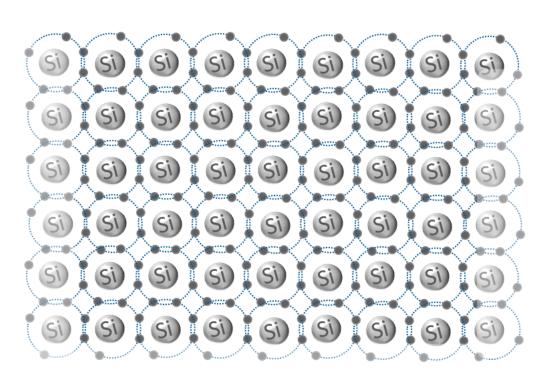

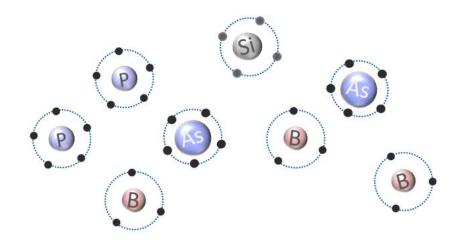

- Dopants are introduced into the silicon via a high-energy beam of ions that is directed at the wafer surface.

- The electrical properties of the silicon wafer are modified by "doping" with selected impurities.

- The most common dopants are boron, phosphorous, and arsenic.

- In most cases, a photo pattern using thick resist is used to prevent the dopants from entering unwanted areas of silicon.

#### **Ion Implantation & Heat Treatment**

After all dopants are introduced/implanted, wafers are generally run through a high temperature heat treatment to **anneal** initial CMOS implants

#### **Ion Implantation & Heat Treatment**

After all dopants are introduced/implanted, wafers are generally run through a high temperature heat treatment to anneal initial CMOS implants

# **Before Anneal**

Micron 35

#### Ion Implantation & Heat Treatment

After all dopants are introduced/implanted, wafers are generally run through a high temperature heat treatment to anneal initial CMOS implants

#### After Anneal

### NW RESIST STRIP [WET PROCESS]

- In the <u>Wet Process Area</u> plasma and wet chemistry are used to remove the photoresist after the implant is complete.

- <u>Metrology:</u>

- There should be no residual resist left on the wafer.

# Wet Process – Wafer Cleaning

- The Wet Etch area uses chemical baths and de-ionized water to remove films and clean wafers to reduce defectivity.

- After every patterning operation, one or more wet process steps are used to remove the leftover photoresist and clean up residual organics, particles, and other forms of contamination.

- Wet process steps make up the largest percentage of the traveler.

- Multiple different chemistries are used to "selectively" remove some materials while leaving critical layers untouched.

Typical Wet Etch Process:

- 1. Wafer is immersed in or sprayed with wet chemicals

- 2. Wet chemicals react with solid film constituents to break them down into solution

- 3. Wafer is immersed in or sprayed with DI water

- 4. DI water rinses away residual by-products and chemicals

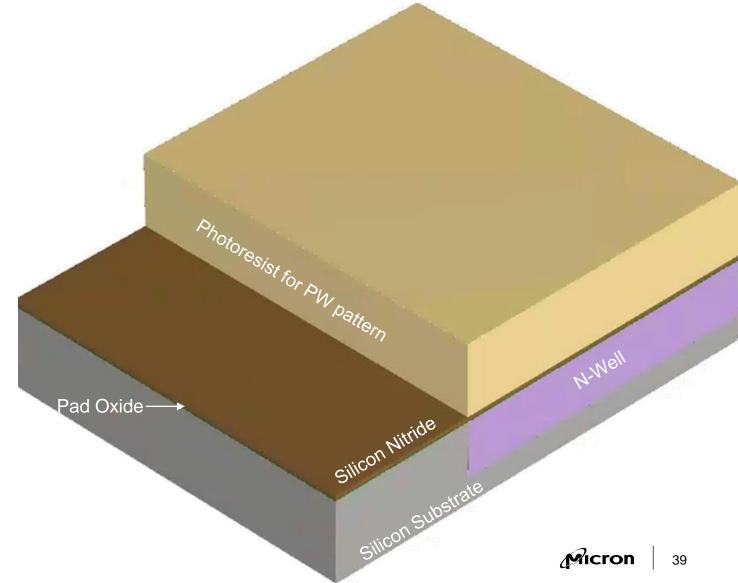

### PW P-WELL PHOTO PATTERN [PHOTO]

- In the <u>Photolithography Area</u> the "PW" mask is used to define a pattern in photoresist. The pattern will open certain areas where P-Wells are needed for the formation of NMOS devices.

- Metrology:

- Resist Thickness: very thick to block implant

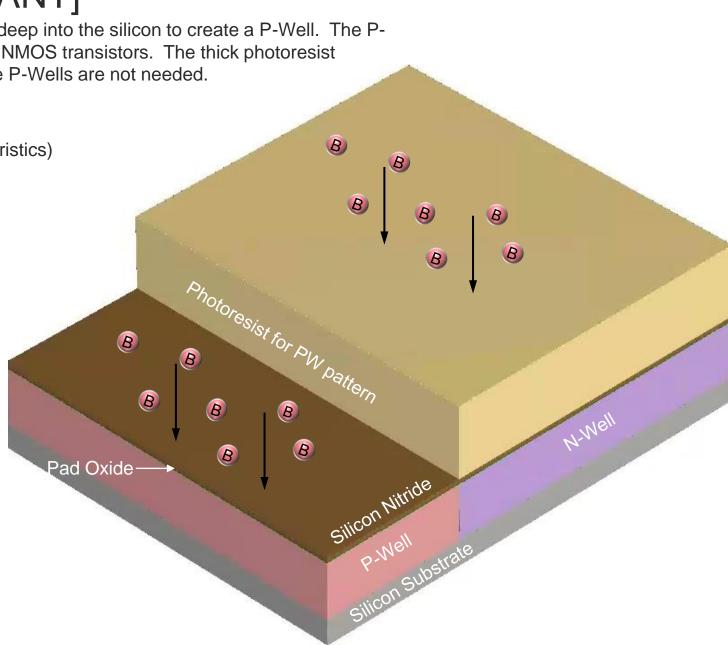

### PW P-WELL IMPLANT [IMPLANT]

- In the <u>Implant Area</u> an ion implanter shoots boron ions deep into the silicon to create a P-Well. The P-Well will provide the background doping needed to form NMOS transistors. The thick photoresist prevents the ions from entering the wafer in areas where P-Wells are not needed.

- <u>Metrology:</u>

- Implant Depth: deep implant

- Implant Dose: Low (needed for transistor characteristics)

Q) What do you think is the next Traveler step?

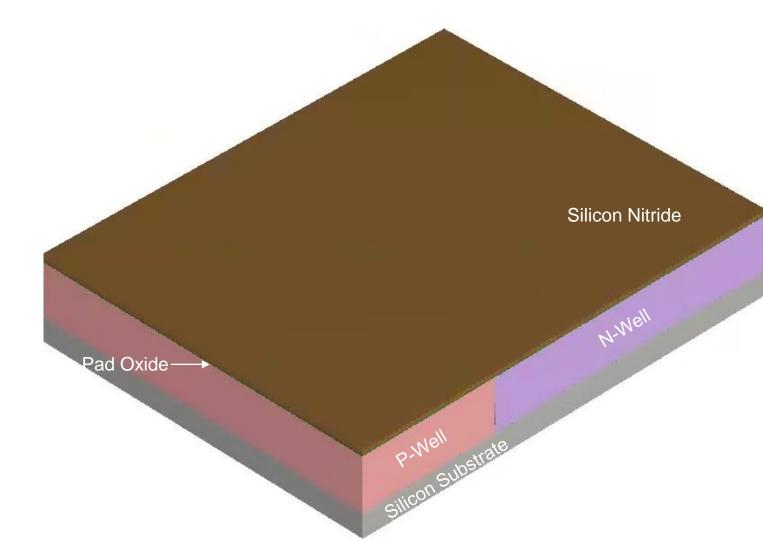

### PW RESIST STRIP [WET PROCESS]

- In the <u>Wet Process Area</u> plasma and wet chemistry are used to remove the photoresist after the implant is complete.

- <u>Metrology:</u>

- There should be no residual resist left on the wafer.

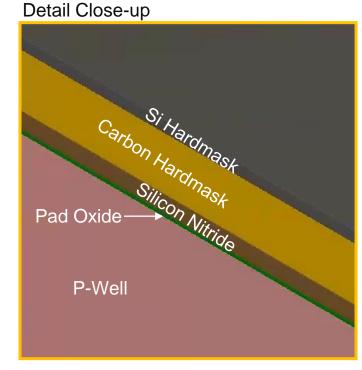

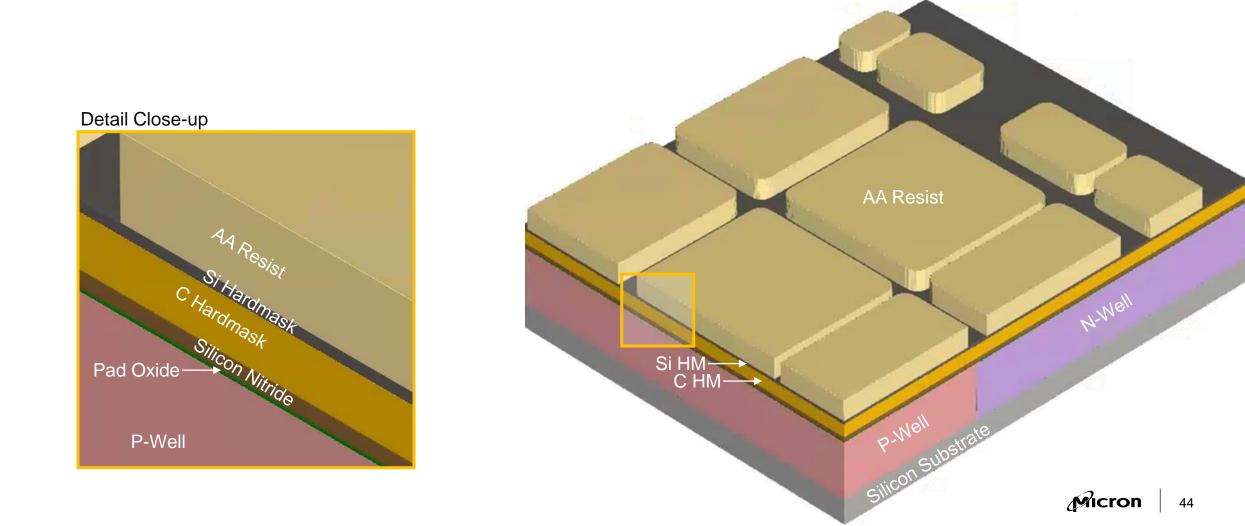

### AA HARDMASK LAYERS DEPOSIT [CHEMICAL VAPOR DEPOSITION (CVD)]

In the <u>CVD Area</u> a thick film of carbon (C) is deposited followed by a thin silicon-based (Si) film.

Together these films comprise a "hardmask" which allows us to etch very small features while keeping the photoresist layer as thin as possible. Hardmasks are prevalent throughout this CMOS flow.

Si HN

P-Well

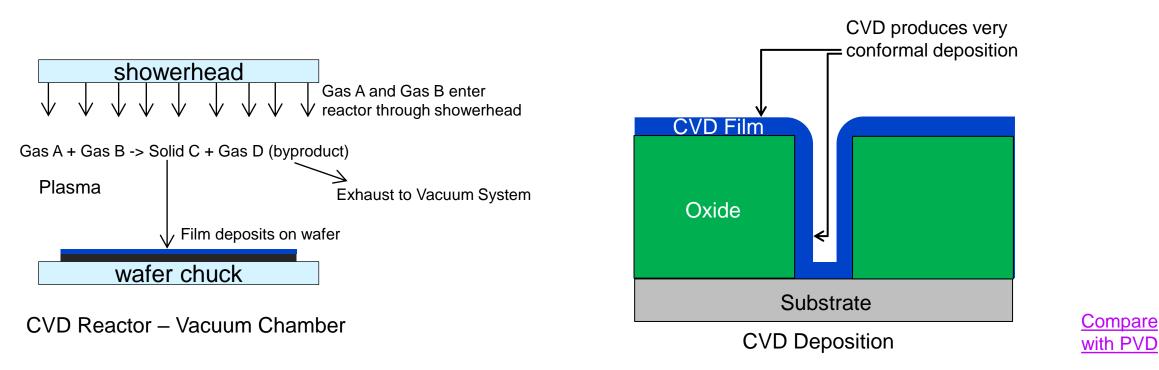

# **Chemical Vapor Deposition (CVD)**

- CVD is used to deposit a variety of insulating and conductive films at multiple places in the Traveler.

- Gases are introduced into a chamber. A solid film, which is a product of the reaction, deposits on the wafer.

- Most CVD processes also use plasma technology (similar to dry etch).

- Compared to other deposition methods, CVD films can be very conformal, allowing us to fill very narrow holes and trenches without creating voids or gaps.

### AA ACTIVE AREAS PHOTO PATTERN [PHOTO]

In the <u>Photolithography Area</u> the "AA" mask is used to define a pattern in photoresist. The pattern defines "active areas" where CMOS devices will be formed. Between the active areas, trenches will be etched into the silicon substrate to provide electrical isolation between devices.

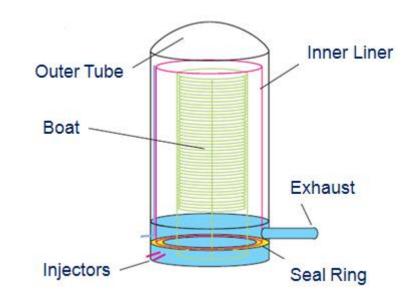

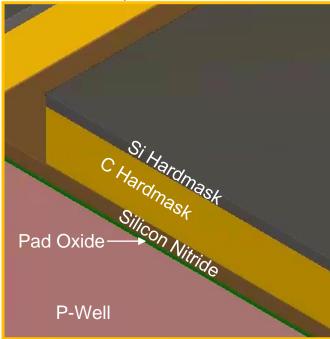

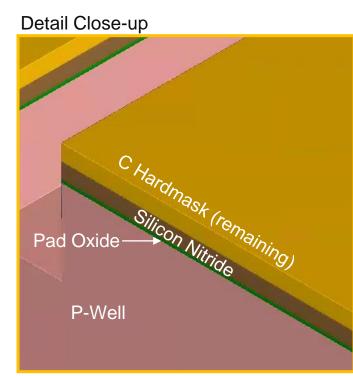

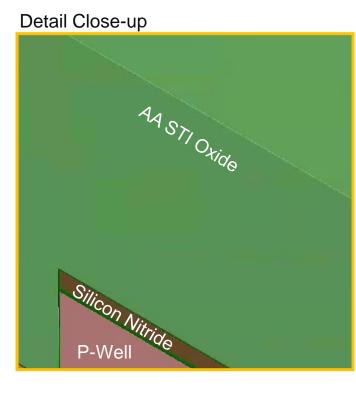

# AA HARDMASK DRY ETCH [DRY ETCH]

- In the <u>Dry Etch Area</u> a plasma process is used to transfer the AA photoresist pattern into the underlying hardmask layers. The hardmask layers will provide a more robust mask for the subsequent trench etch than photoresist.

- Notes:

- This step is also known as "Dry Develop"

- The photoresist is completely etched away in this step.

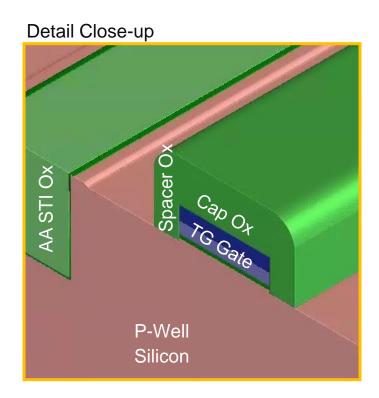

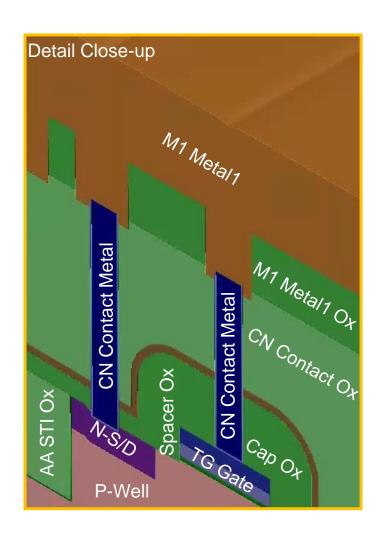

**Detail Close-up**

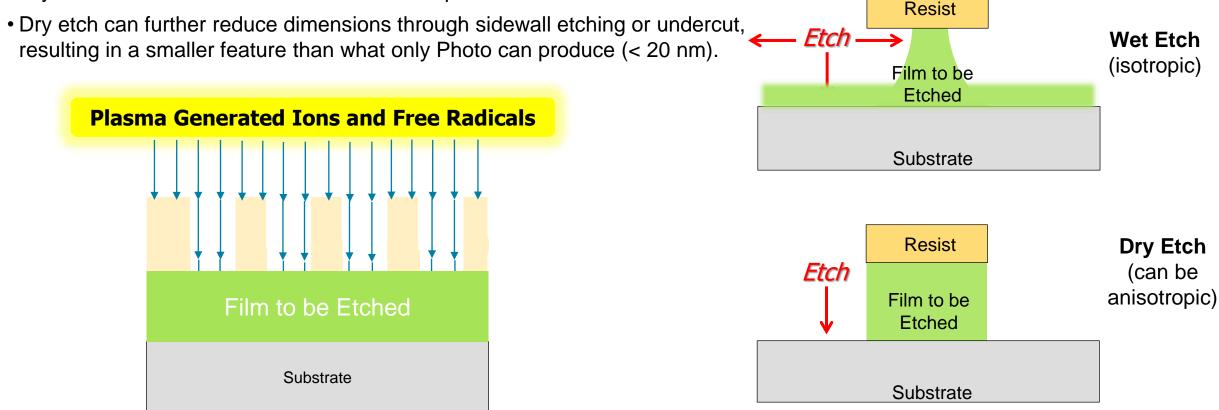

# **Dry Etching**

- The Dry Etch area **removes** (etches) films using plasma (ionized gases). Dry Etch usually processes wafers after a temporary mask has been previously patterned, e.g. photoresist or a hardmask. The mask protects some regions of the wafer. Dry Etch only removes films from the unprotected regions. Very fine and precise patterns can be etched into films.

- Dry etch utilizes plasma technology to permanently transfer a mask pattern into the underlying layer(s).

- Wet processing can also be used for patterning, but wet process is isotropic while dry etching can be vertical (anisotropic). Dry Etch allows for much more accurate and precise feature definition.

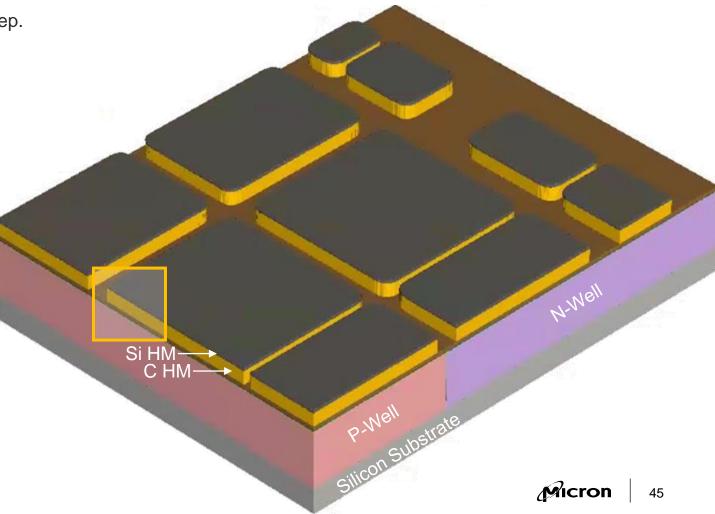

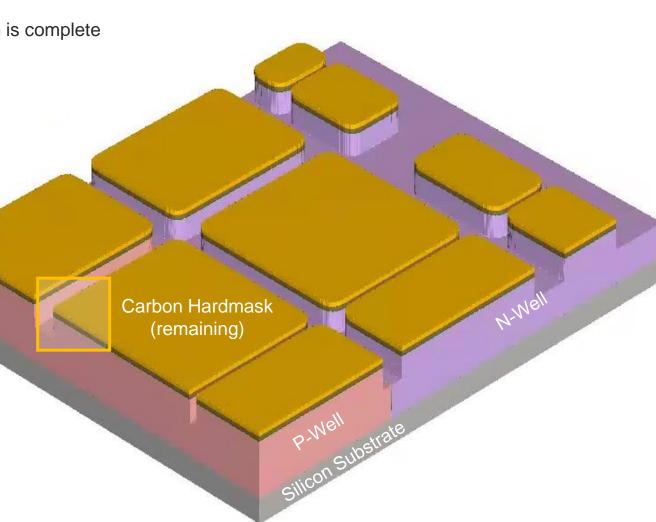

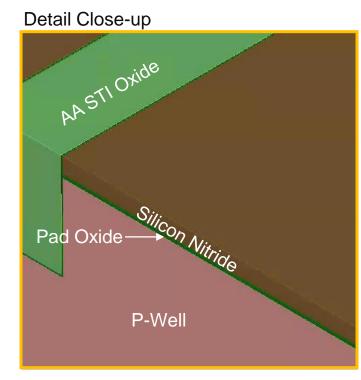

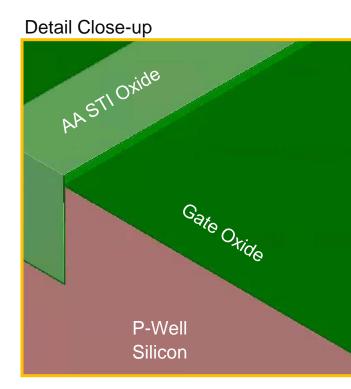

# AA STI DRY ETCH [DRY ETCH]

- In the <u>Dry Etch Area</u> a second plasma process is used to etch trenches into the silicon wafer. For this process the mask is the Si hardmask and the carbon hardmask. These trenches will be filled with oxide and will provide electrical isolation between adjacent active areas.

- Notes:

- STI stands for "Shallow Trench Isolation"

- > Some of the carbon hardmask layer remains after this etch is complete

Q) What do you think is the next Traveler step?

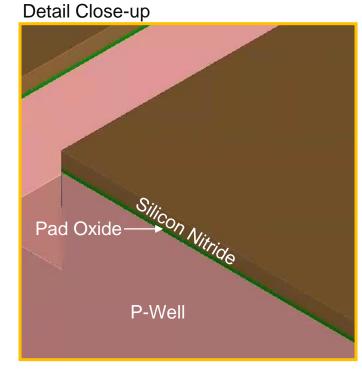

### AA RESIST STRIP [WET PROCESS]

- In the <u>Wet Process Area</u> plasma and wet chemistry are used to remove the remaining carbon hardmask after the trench etch is complete (similar recipe used to remove photoresist)

- Metrology:

- There should be no residual carbon left on the wafer.

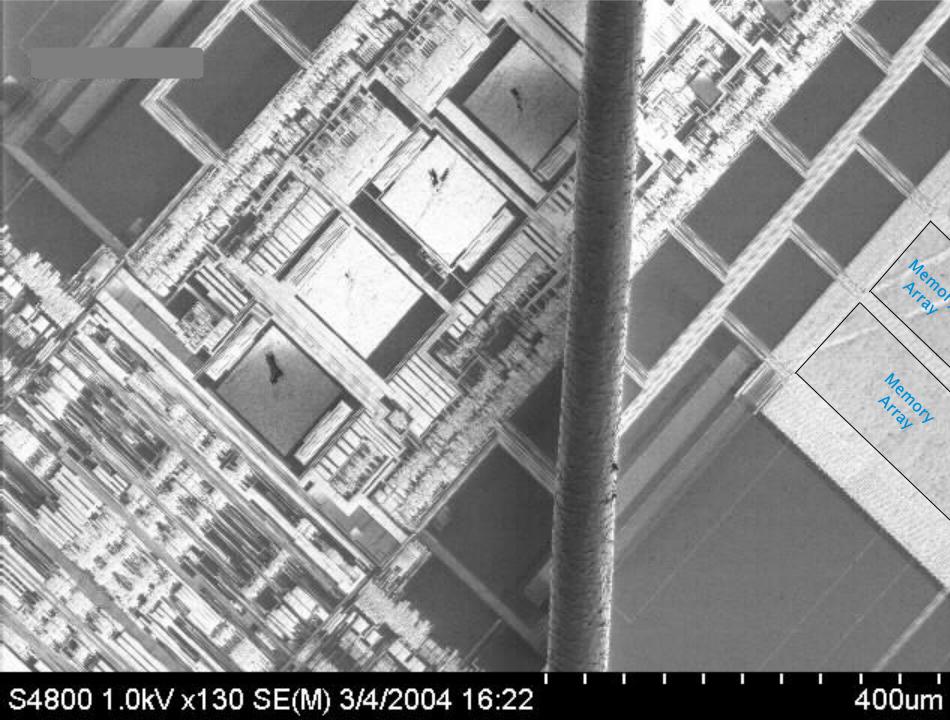

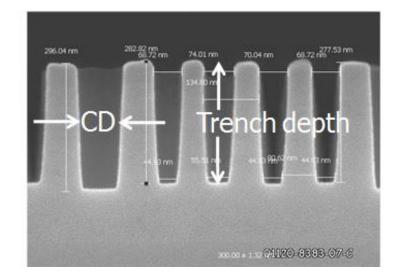

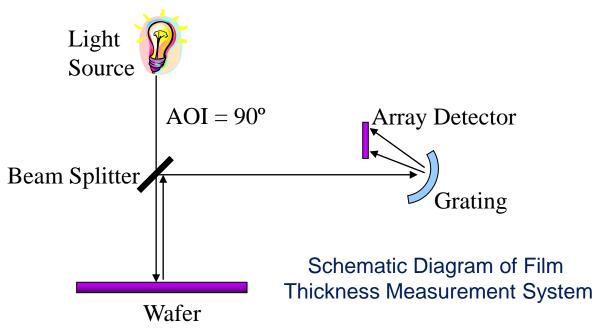

# Metrology

- The Metrology area takes measurements that evaluate the results of process operations.

- Examples of measurements are film thicknesses, critical dimensions (CD's), lithography overlay, film resistivity, surface planarity, composition, and stress.

- At right is a cross section image of a wafer where several critical dimensions (CDs) were taken using a scanning electron microscope (SEM).

- Below is a schematic diagram of a system used to measure the thickness of very thin films. This technique uses the principle of optical interference.

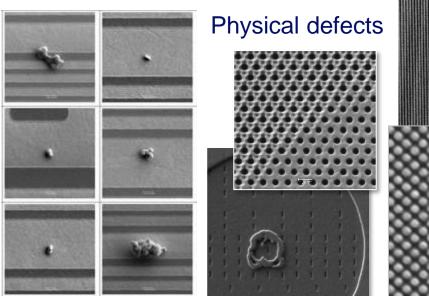

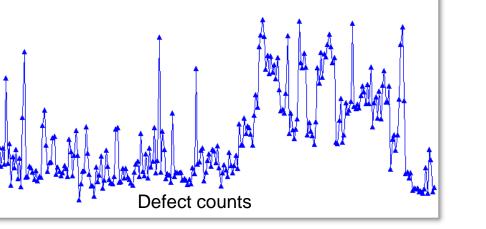

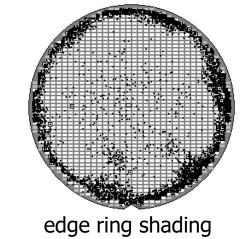

# **Real-Time Defect Analysis (RDA)**

- The Real-Time Defect Analysis (RDA) area inspects wafers for defects at critical points in the manufacturing process.

- The RDA area monitors in-line wafers and provides critical data collection and analysis services to fab process areas

- The process areas use the information that RDA provides to reduce defectivity on the wafers

Metro & RDA do not alter the structural or electrical characteristics, however, for processing wafers from start to finish **THEY ARE OUR EYES** to what is happening on the wafers. **THEY ARE CRITICAL** for design, layout, reticle, process and equipment improvements to maximize yield, quality, and performance.

#### Defect Wafer Maps

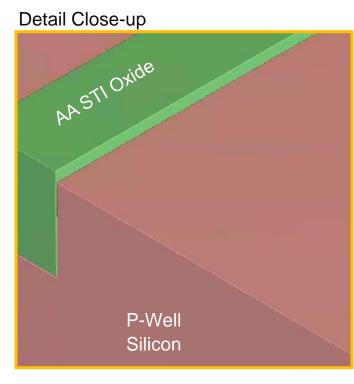

# AA STI OXIDE DEPOSIT [CVD]

In the <u>CVD Area</u> a thick film of silicon dioxide is deposited to fill the trenches. Only the oxide in the trenches is needed, so the unwanted surface oxide will be removed in the next Traveler step.

Q) What do you think is the next Traveler step?

AASTIOXIDE

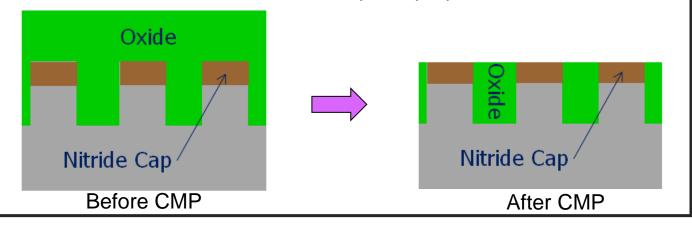

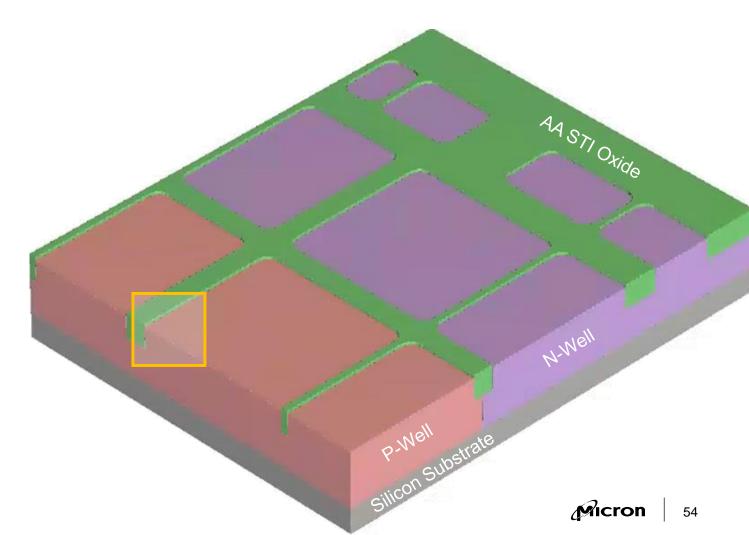

### AA STI OXIDE CMP [CHEMICAL MECHANICAL PLANARIZATION]

- In the **<u>CMP Area</u>** a polishing process is used to remove the unwanted oxide on the surface, leaving the trenches filled with oxide.

- <u>Note</u>: The silicon nitride film, deposited near the beginning of the flow, effectively stops the CMP process. This process is referred to as a "Stop on Nitride (SON)" process.

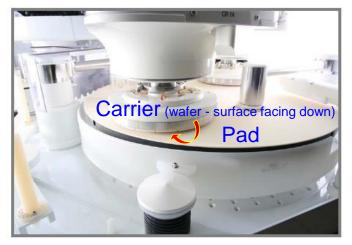

# **Chemical Mechanical Planarization (CMP)**

- CMP is used to reduce or eliminate topography on the wafer surface. A planar surface is necessary for photo to print patterns at very small feature sizes.

- CMP is also used to remove excess surface films after they have been deposited.

- CMP uses a polishing pad and a chemical slurry made of fine abrasive particles suspended in a dilute chemical solution to perform the polishing process.

- Like wet etch and dry etch, CMP can selectively polish some films while leaving others untouched.

CMP "**Stop on Nitride**" Process: on-tool sensors allows this process to detect the different hardness or optical properties of materials

### AA STI NITRIDE WET ETCH [WET PROCESS]

- The nitride film is no longer needed, so in the <u>Wet Process Area</u> wet chemicals are used to completely remove the nitride with minimal impact to the exposed oxide or silicon layers.

- A second wet chemical process removes the original Pad Oxide, exposing bare silicon.

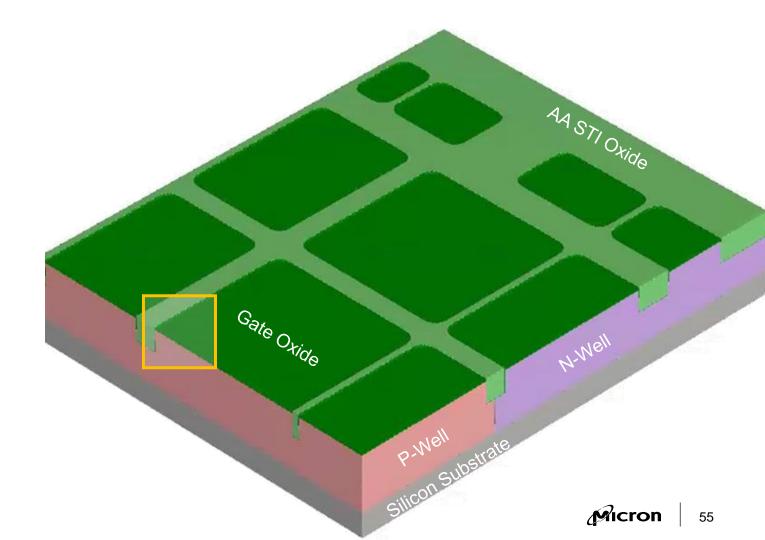

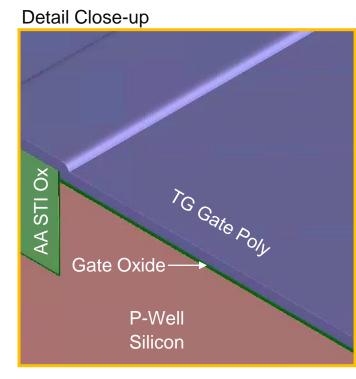

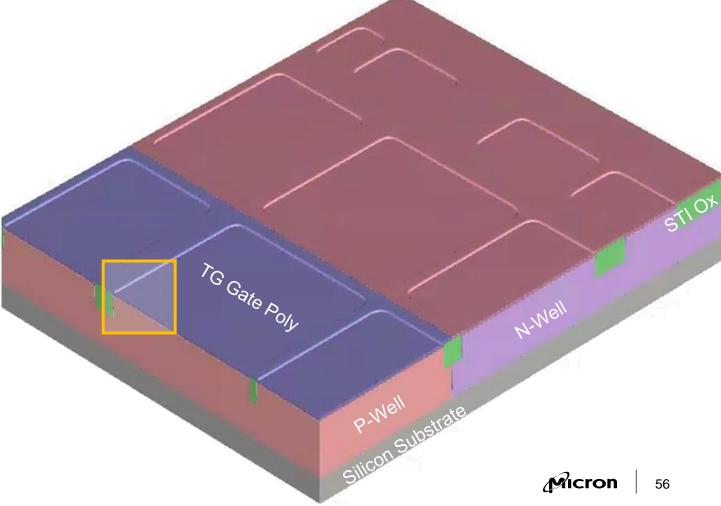

### TG GATE OXIDE GROWTH [DIFFUSION]

In the <u>Diffusion Area</u> a thin film of high-quality silicon dioxide is grown on the surface of the silicon wafer. This oxide will be an important part of the gates of the CMOS transistors: the gate oxide.

# TG GATE POLYSILICON DEPOSITION [DIFFUSION]

- In the <u>Diffusion Area</u> a polycrystalline silicon film (known as "poly") is deposited on top of the gate oxide. The poly will be the electrodes of the transistor gates.

- <u>Note</u>: The poly is doped N-type or P-type, shown as purple (N-type) or pink (P-type) in the diagram, as needed for optimal performance of the CMOS devices. The doping will be accomplished by a series of implants (not described in this document).

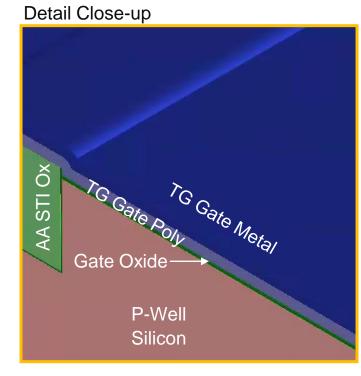

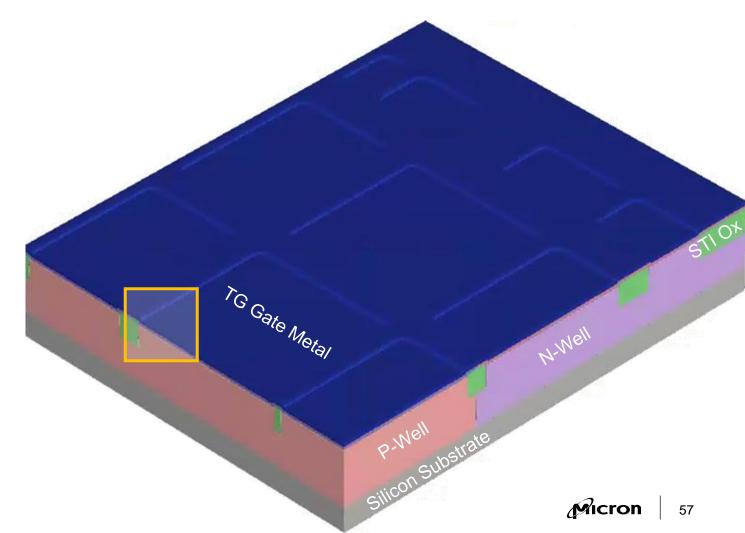

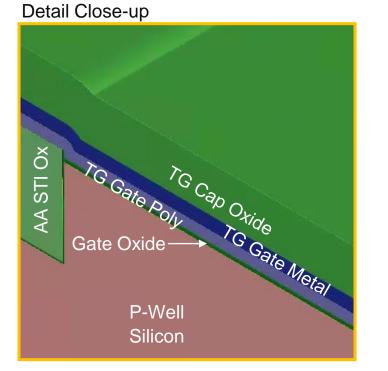

### **TG GATE METAL DEPOSIT** [PHYSICAL VAPOR DEPOSITION (PVD)]

- In the **PVD Area** a metal film is deposited on top of the polysilicon film. This will form the conductive part of the transistor gates.

- Note: Several different types of metals may be used for this step

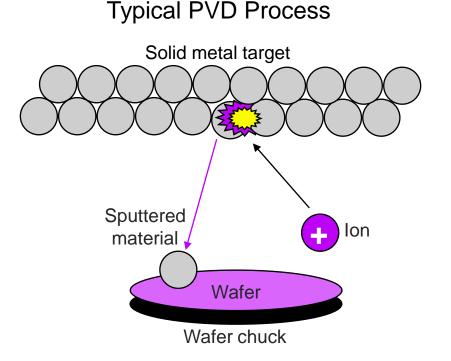

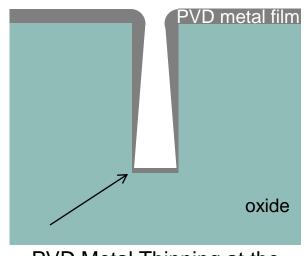

# **Physical Vapor Deposition (PVD)**

- Many of the metal films in the process are deposited using Physical Vapor Deposition (PVD) technology (also known as "sputtering").

- lons bombard a metal target. The sputtered metal deposits on the wafer.

- The process involves little or no chemistry, and takes place at low (or room) temperature.

- PVD deposits a wide variety of metal films quickly and at relatively low cost.

- PVD films do not deposit as conformally as CVD films, so they cannot be used to fill deep contacts or trenches.

PVD Metal Thinning at the Bottom of a Deep Contact

Compare with CVD

# TG CAP OXIDE DEPOSIT [CVD]

- In the **CVD Area** a thick film of silicon dioxide is deposited to protect the gate metal layer from corrosion and damage.

- <u>Note</u>: Some technologies use silicon nitride for this purpose.

- This film is called Cap Oxide in this case.

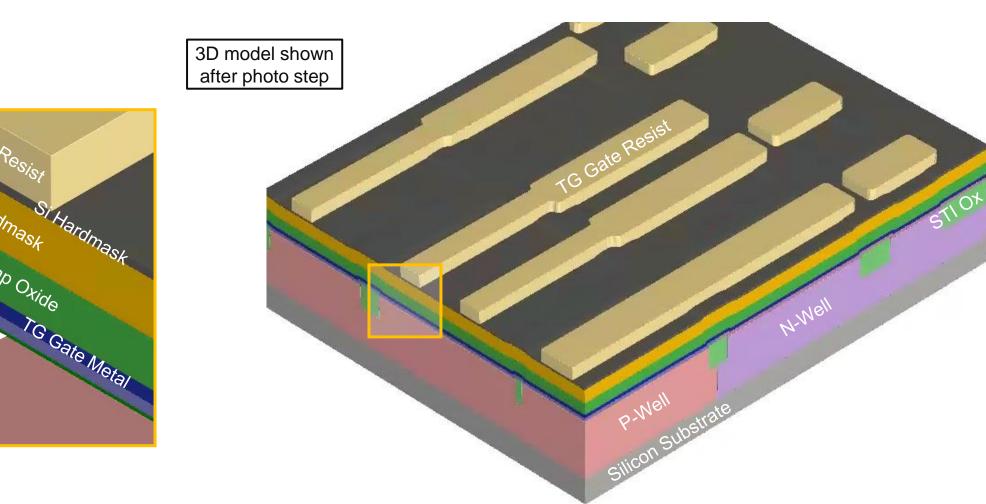

### **TG HARDMASK LAYERS DEPOSIT**

GRes

CHardmask

TG Cap Oxide

G Gate Poly

P-Well Silicon

Gate Oxide

**Detail Close-up**

AA STI Ox

Deposit hardmask layers for patterning the transistor gates.

### **TG GATE PHOTO PATTERN**

The "TG" mask is used to define the pattern in photoresist for the gates of the CMOS devices. The pattern also electrically connects the transistor gates to each other.

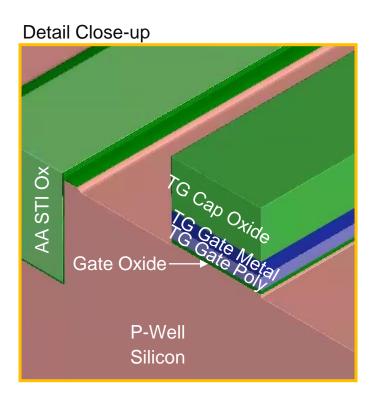

### **TG HARDMASK DRY ETCH**

• A plasma process is used to transfer the TG photoresist pattern into the underlying hardmask layers.

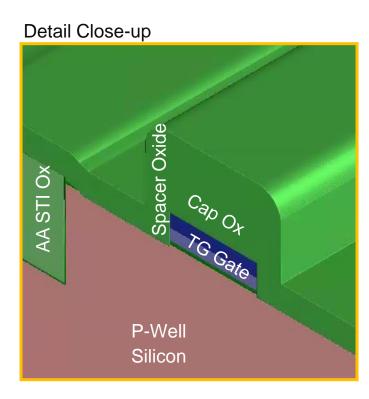

### TG GATE DRY ETCH

• A second plasma process is used to etch away the unwanted gate stack layers, leaving behind the gates.

Plasma and wet chemistry are used to remove the remaining carbon after the gate etch is complete.

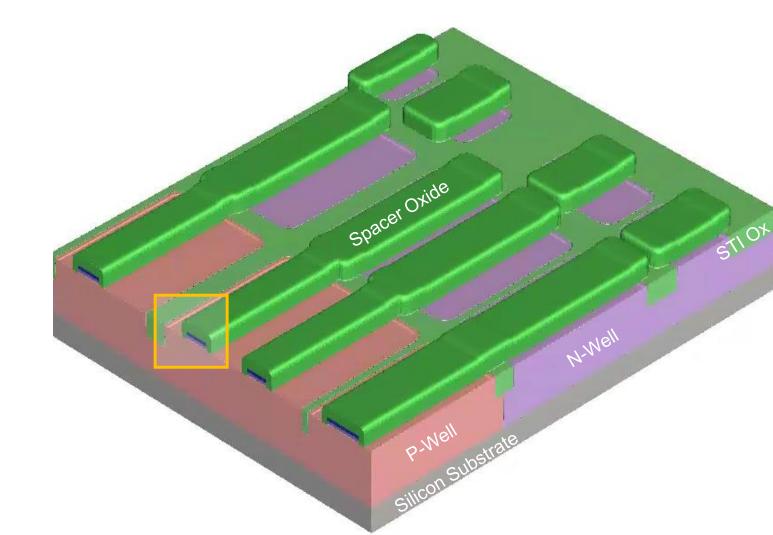

### TG SPACER OXIDE DEPOSIT [CVD]

• A thin film of silicon dioxide is deposited to form a spacer on the sidewalls of the gate. The spacer will protect the gate metal from corrosion and is used to ensure the source/drain implants will be correctly aligned to the gate.

### TG SPACER OXIDE DRY ETCH [DRY ETCH]

A specially-designed plasma process is used to etch the spacer oxide from the horizontal surfaces while the oxide remains intact on the sidewalls of the gates.

#### NA N-SOURCE/DRAIN PHOTO PATTERN

The "NA" mask opens up the NMOS transistors to receive the N source/drain implant. A thick resist is used to block the implant in the areas that should not receive the implant.

#### NA RESIST STRIP [WET PROCESS]

N-Source/Drain

Spacer Oxide

Plasma and wet chemistry are used to remove the photoresist after the implant is complete

3D model shown before resist strip

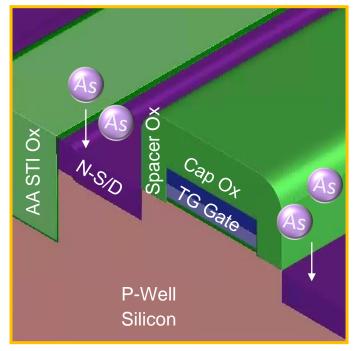

#### NA N-SOURCE/DRAIN IMPLANT

- An ion implanter shoots a high dose of arsenic ions into the silicon near the surface to form the sources and drains of the NMOS transistors.

- <u>Note:</u> The gate and spacers confine the implant to the S/D regions only. This is known as a "self-aligned" implant.

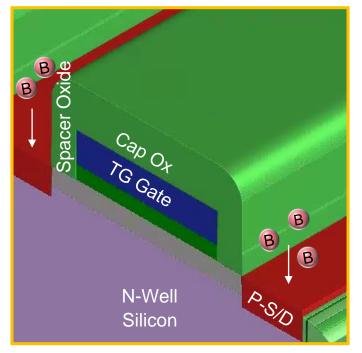

#### **PA P-SOURCE/DRAIN PHOTO PATTERN**

The "PA" mask opens up the PMOS transistors to receive the P source/drain implant. A thick resist is used to block the implant in the areas that should not receive the implant.

#### PA RESIST STRIP [WET PROCESS]

Spacer Oxide

P-Source/Drail

Plasma and wet chemistry are used to remove the photoresist after the implant is complete.

3D model shown before resist strip

1-Wel

-Nell

#### **PA P-SOURCE/DRAIN IMPLANT**

- An ion implanter shoots a high dose of boron ions into the silicon near the surface to form the sources and drains of the PMOS transistors.

- <u>Note:</u> The gate and spacers confine the implant to the S/D regions only. This is known as a "self-aligned" implant.

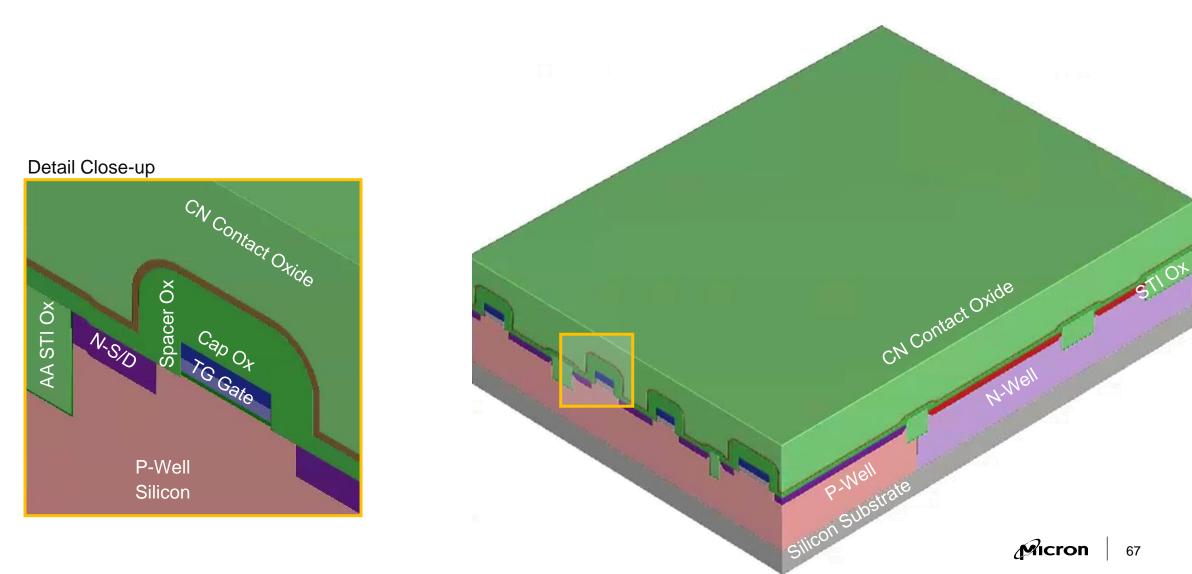

### CN CONTACT OXIDE DEPOSIT [CVD]

• A thick film of silicon dioxide is deposited to protect the CMOS transistors.

Q) What do you think is the next Traveler step?

Micron

66

CN Contact Oxide

P-Well Substrate

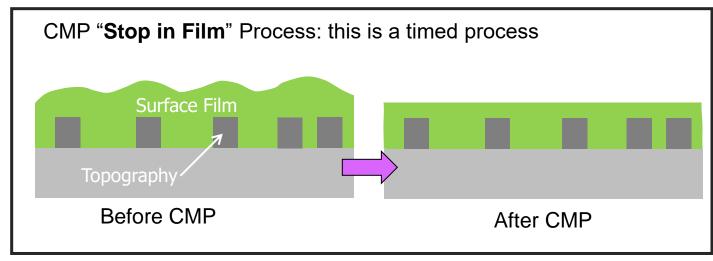

# CN CONTACT OXIDE CMP [CMP]

• A polishing process is used to planarize the wafer surface to improve photo patterning of contacts. In this case a CMP "Stop in Film" timed process is used.

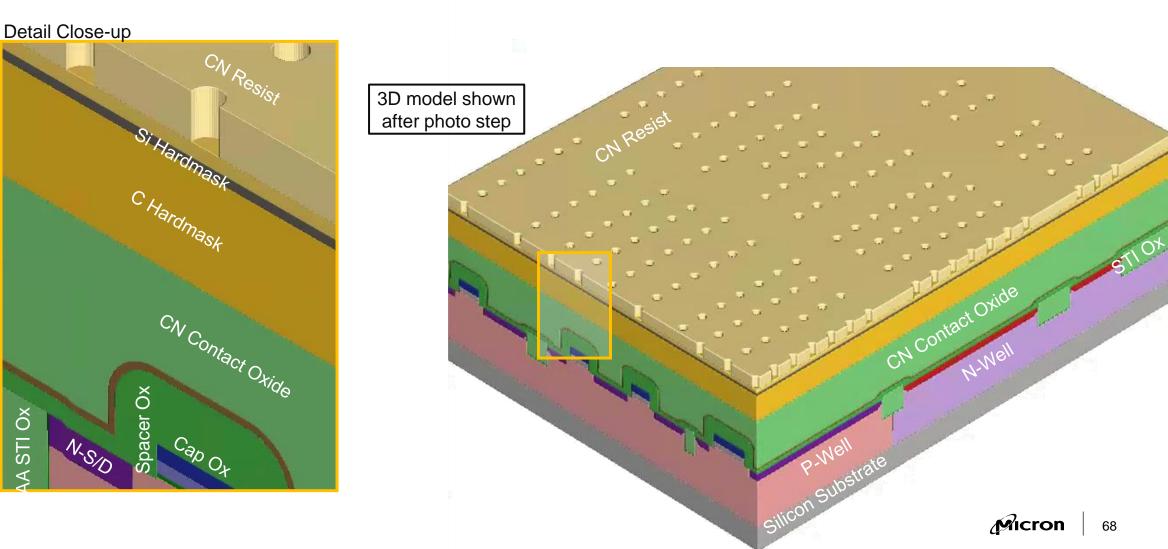

### **CN HARDMASK LAYERS DEPOSIT**

Deposit hardmask layers for patterning the contacts.

A STI Ox

### **CN CONTACT PHOTO PATTERN**

The "CN" mask is used to define the pattern in photoresist for the contacts. The contacts will provide vertical conductive paths (wires) from the CMOS devices to the first interconnect level.

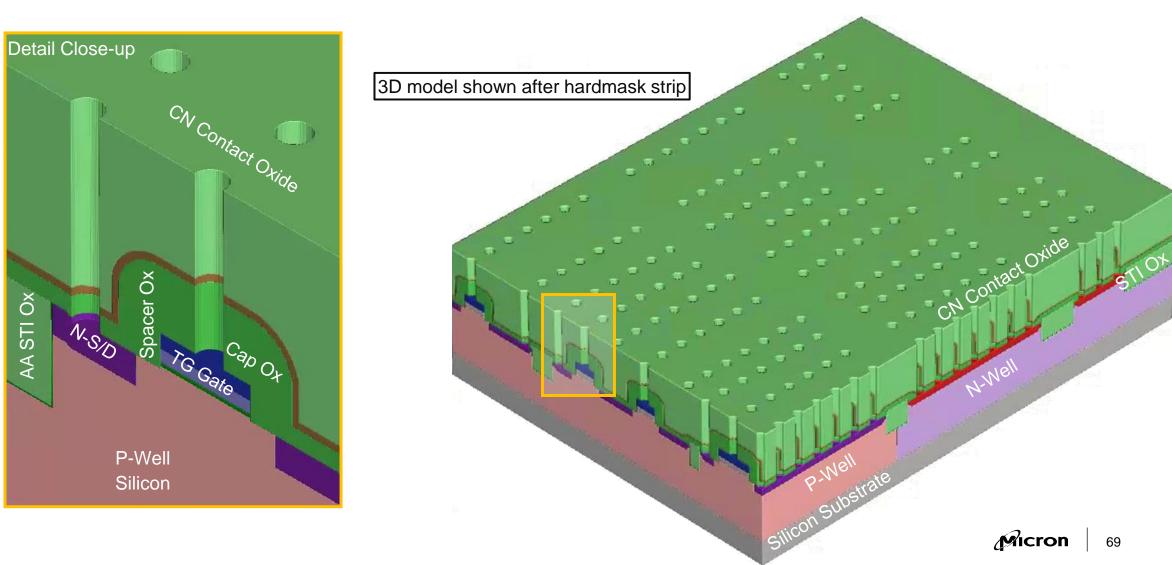

### **CN CONTACT DRY ETCH**

A plasma process is used to etch holes in the hardmask layers, and down through the oxide films. The etch has selectivity to stop on the sources and drains (silicon), and gates (metal).

### **CN RESIST STRIP** [WET PROCESS]

Plasma and wet chemistry are used to remove the remaining carbon after the contact etch is complete.

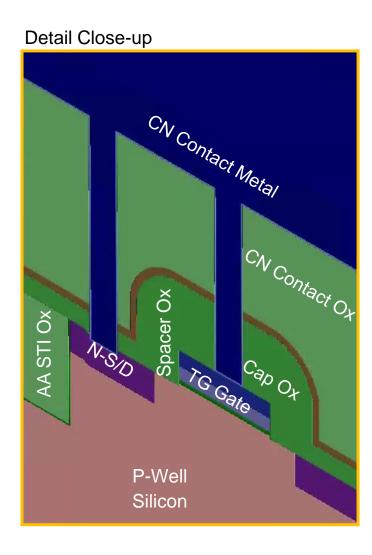

### CN CONTACT METAL DEPOSIT [CVD]

• A conductive metal layer is deposited to fill the contact holes. CVD tungsten (W) is chosen to completely fill the holes without creating voids.

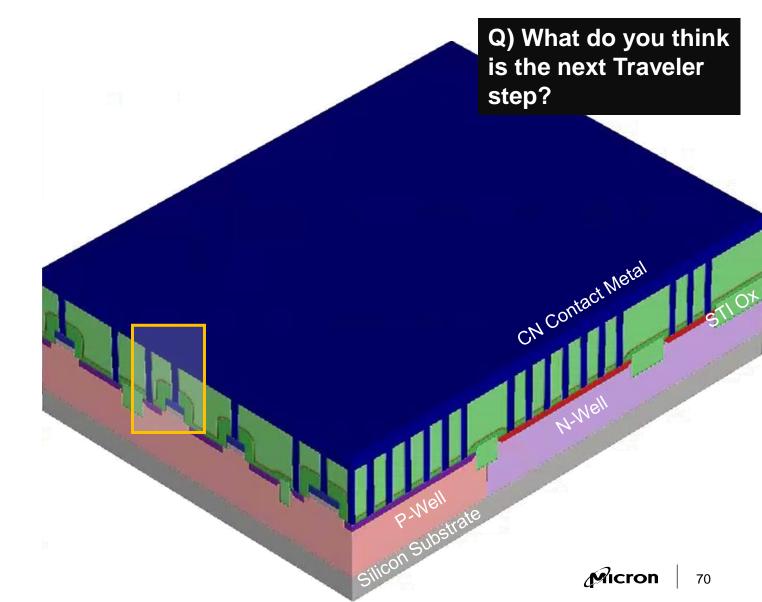

### **CN CONTACT METAL CMP** [CMP]

• A polishing process is used to remove all of the metal on the surface (known as "overburden"), leaving only the contacts filled with metal.

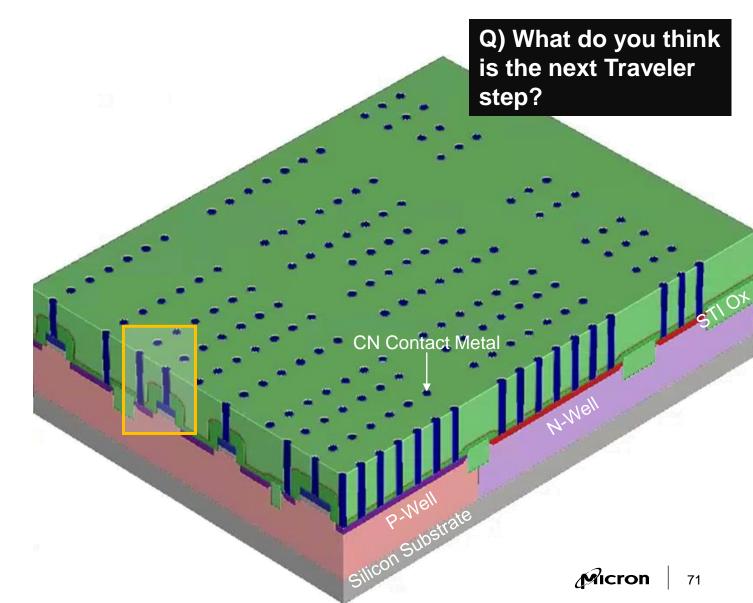

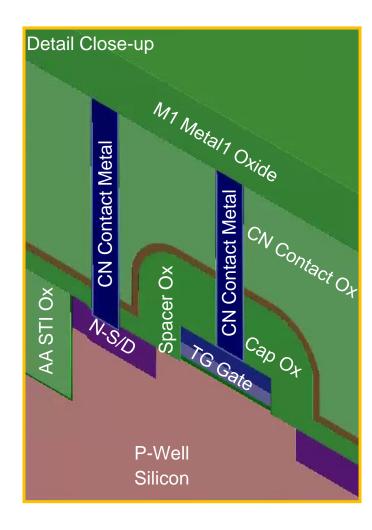

### M1 METAL1 OXIDE DEPOSIT [CVD]

- A thick film of silicon dioxide is deposited to serve as the foundation for the formation of the first metal interconnect layer.

- <u>Note</u>: Most chips will have multiple levels of metal interconnects. In this example, we will only show one level.

### **M1 HARDMASK LAYERS DEPOSIT**

M1 Metal 1 Oxide

Contact Metal

õ

Bieg D1 Spacer

CN Contact O

Cap Of

**CN Contact Metal**

N.S.D

P-Well

AA STI Ox

Deposit hardmask layers for patterning the metal interconnects. ►

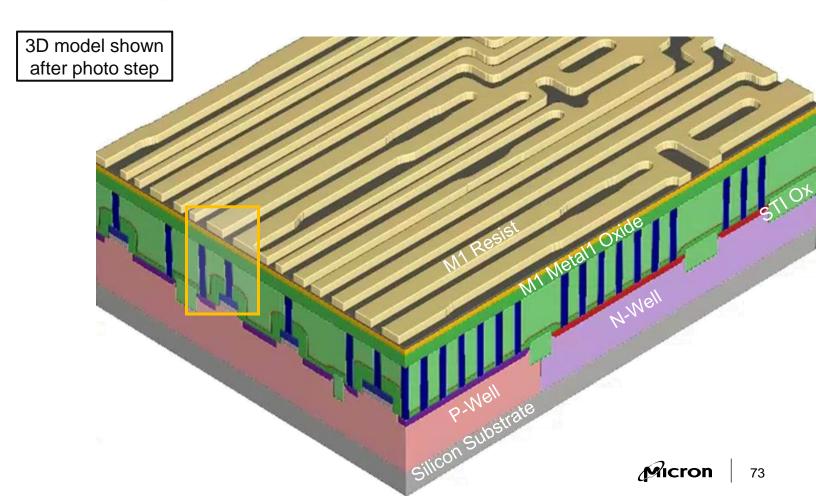

### **M1 METAL1 PHOTO PATTERN**

The "M1" mask is used to define the pattern in photoresist for the ► first level of metal interconnects. The interconnects will provide horizontal conductive paths (wires) connecting the various parts of the circuit.

### M1 METAL1 DRY ETCH

A plasma process is used to etch trenches in the M1 oxide layer. The etch must be deep enough to expose the top of the CN metal contacts.

3D model shown after resist strip

#### Detail Close-up

### M1 RESIST STRIP [WET PROCESS]

Plasma and wet chemistry are used to remove the remaining carbon after the trench etch is complete.

M1 Metal1 Oxide

Q) What do you think is the next Traveler step?

Micron

74

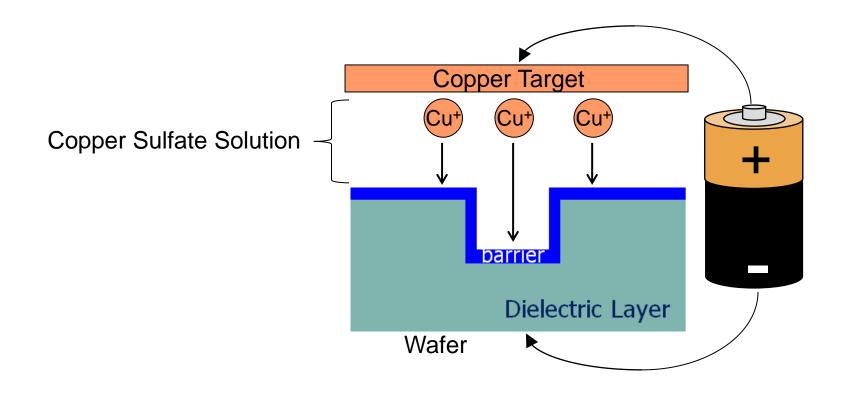

### M1 METAL1 METAL DEPOSIT [WET PROCESS]

A conductive metal layer is deposited to fill the trenches. Copper (Cu) is chosen for low resistivity. A special wet chemical process known as "electroplating" is used to deposit the copper.

# Wet Process – Electroplating

- Copper is uniquely deposited via electroplating.

- The wafer is immersed in a solution of copper sulfate. An electric current is forced through the solution, and copper ions are transported from a target to the wafer.

- Electroplating effectively fills deep trenches and is more cost effective than PVD for thick copper layers.

### M1 METAL1 CMP [CMP]

- A polishing process is used to remove all of the overburden metal on the surface, leaving the trenches filled with copper.

- <u>Note</u>: The process of forming metal interconnects by filling trenches with metal and then using CMP to remove the surface metal is known as "damascene". (Due to resembling the ancient metal handicrafts made in Damascus, Syria)

# BP PASSIVATION DEPOSIT [CVD]

- A thick film of silicon nitride, known as "passivation", is deposited to protect the fragile circuits and devices from moisture, contamination, and damage.

- Large holes (not shown) will be etched into the passivation to allow for electrical testing and to connect the die circuits to the package.

2 Passivation Nitride

# Educator Hub

© 2020-2024 Micron Technology, Inc. All rights reserved. Information, products, and/or specifications are subject to change without notice. All information is provided on an "AS IS" basis without warranties of any kind. Statements regarding products, including statements regarding product features, availability, functionality, or compatibility, are provided for informational purposes only and do not modify the warranty, if any, applicable to any product. Drawings may not be to scale. Micron, the Micron logo, and other Micron trademarks are the property of Micron Technology, Inc. All other trademarks are the property of their respective owners.